基于FPGA和LabView的遙測(cè)信號(hào)模擬源設(shè)計(jì)

摘要:基于FPGA和LabView設(shè)計(jì)了用于某遙測(cè)組件測(cè)試的專用設(shè)備。運(yùn)用DDS技術(shù)實(shí)現(xiàn)傳輸速率可變的LNDS信號(hào),并使用LabView圖形編程工具,實(shí)現(xiàn)了數(shù)字信號(hào)源的交互界面,可以產(chǎn)生由上住機(jī)程控信號(hào)傳輸速率和數(shù)據(jù)內(nèi)容可變的LVDS信號(hào)。

關(guān)鍵詞:FPGA;LabView;DDS;LVDS

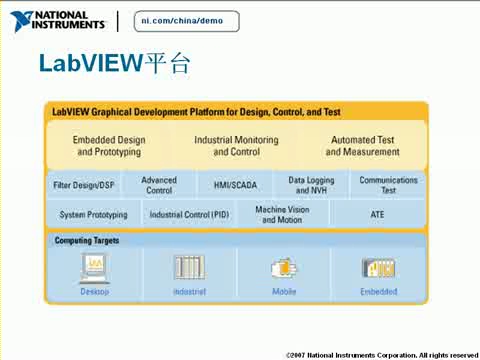

多種高新技術(shù)應(yīng)用于遙測(cè)設(shè)備中,使得待測(cè)信號(hào)種類繁多,測(cè)試量增大,而且測(cè)試時(shí)間緊迫、環(huán)境復(fù)雜多變等諸多因素對(duì)測(cè)試系統(tǒng)提出了更高要求,不僅要求測(cè)試自動(dòng)化、快速化,而且要求測(cè)試系統(tǒng)結(jié)構(gòu)緊湊堅(jiān)固,抗干擾能力強(qiáng),具備在復(fù)雜環(huán)境下工作的能力。基于總線技術(shù)的虛擬儀器測(cè)試系統(tǒng)架構(gòu),能夠滿足上述要求。PCI總線以其速度高、可靠性強(qiáng)、成本低及兼容性好等性能,在各種總線標(biāo)準(zhǔn)中占有重要地位。FPGA器件具有編程方便、速度快、開發(fā)費(fèi)用低、周期短等特點(diǎn),受到了廣大設(shè)計(jì)人員的青睞。DDS頻率合成技術(shù)使輸出信號(hào)受頻率控制碼和相位控制碼以及參考時(shí)鐘控制,容易實(shí)現(xiàn)調(diào)頻、調(diào)相,輸出信號(hào)具有高速的頻率轉(zhuǎn)換時(shí)間、極高的頻率分辨率和低相位噪聲等優(yōu)點(diǎn)。基于上述特點(diǎn),本設(shè)計(jì)運(yùn)用DDS技術(shù)在FPGA片內(nèi)實(shí)現(xiàn)可變頻率方波發(fā)送固定格式數(shù)據(jù),為了實(shí)現(xiàn)一個(gè)基于虛擬儀器平臺(tái)的遙測(cè)信號(hào)模擬源的設(shè)計(jì),下位機(jī)與PC通過I/O卡連接。

1 DDS原理及DDS和LVDS在FPGA中實(shí)現(xiàn)

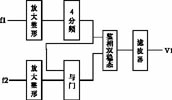

DDS的原理是利用信號(hào)的相位與時(shí)間成線性關(guān)系的特性,通過查表的方式得到信號(hào)的瞬時(shí)值,從而實(shí)現(xiàn)頻率合成。DDS的基本原理框圖,如圖1所示,輸出正弦信號(hào)頻率分辨率為△f=fmin=fclk/2N,其中,fCLK為輸入時(shí)鐘頻率;N為累加器的寬度;輸出頻率為fo=fclk×K/2N,K為頻率字的輸入值。本次芯片采用Altera公司的CycloneⅡEP2CSQ208C8,設(shè)計(jì)采用原理圖和Verilog HDL相結(jié)合的辦法實(shí)現(xiàn),本設(shè)計(jì)中只需在FPGA內(nèi)部得到可變頻率范圍4~8 MHz的方波,所以不需要D/A和低通濾波器。

相位累加器采用流水線結(jié)構(gòu),即在長(zhǎng)延時(shí)的邏輯功能塊中插入觸發(fā)器,使復(fù)雜的邏輯分步完成,減小每個(gè)部分的處理延時(shí),從而使系統(tǒng)穩(wěn)定地運(yùn)行在較高的頻率上。

方波波形存儲(chǔ)器直接調(diào)用FPGA芯片內(nèi)部的ROM(2 048×1)模塊,前1 024個(gè)點(diǎn)為0,后1 024個(gè)點(diǎn)為1。為了保證一個(gè)地址位對(duì)應(yīng)一個(gè)ROM地址,只截取相位累加器22位地址線的高11位與ROM的11位地址線相連。

低壓差分信號(hào)(Low Voltage Differential Signaling,LVDS)采用極低的電壓擺幅高速差動(dòng)傳輸數(shù)據(jù),可以實(shí)現(xiàn)點(diǎn)對(duì)點(diǎn)或一點(diǎn)對(duì)多點(diǎn)的連接。圖2所示為CycloneⅡ器件與INDS接口電路,由差分信號(hào)發(fā)送器、差分信號(hào)互連器、差分信號(hào)接受器組成。在實(shí)際設(shè)計(jì)中,要實(shí)現(xiàn)一個(gè)LVDS發(fā)送和接收,只需要在MegaWizard中調(diào)用Altlvds并進(jìn)行定制即可。

評(píng)論