基于SOPC基本信號產生器的設計與實現

2.2 FPGA硬件設計

FPGA硬件設計是建立在電路板設計基礎上的對FPGA芯片功能的設計,將一些可以在電路板上實現的功能在FPGA內部通過采用硬件描述語言或搭建模塊的方式來實現,減少了上層設計的工作量以及系統硬件的風險。通常本層設計是通過通用計算機平臺上的可視化編程軟件實現的,本設計采用Altera公司的Quartus II 8.1系列設計工具。

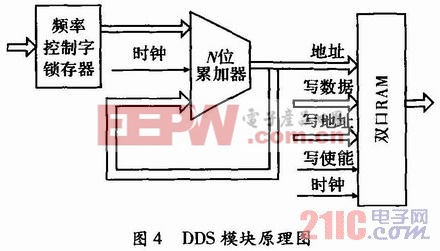

2.2.1 DDS模塊設計

如圖4所示,頻率控制字鎖存器保存頻率設置字M。雙口RAM的寫地址、寫數據以及寫使能端口完成對RAM中1 024 Byte數據的更新,N位累加器輸出結果的高10位作為雙口RAM的讀地址。在系統時鐘fclk的作用下累加器根據頻率控制字M輸出連續變化或跳躍變化的地址,雙口RAM循環輸出相應地址單元中的8位數據,此8位數據接到DAC輸入口。本文引用地址:http://www.104case.com/article/191245.htm

假設雙口RAM中存放一個周期的正弦信號數據,那么此時DAC輸出的正弦信號的頻率fout=fclk×M/2N,同理,當雙口RAM中存放的是方波或者三角波數據時,DAC也會輸出相應頻率的信號。

模塊中32位頻率控制字鎖存器,是用VerilogHDL語言實現的,并生成自定義模塊以供上層原理圖調用。N位累加器和雙口RAM是利用Quar-tus II8.1中的MegaWizard Plug-IN manager定制實現。

2.2.2 定制Nios II CPU

32位的Nios II軟核是該基本信號發生器的核心模塊,主要用于人機界面的控制、鍵盤值的讀取以及控制DDS模塊輸出信號的頻率和樣式。

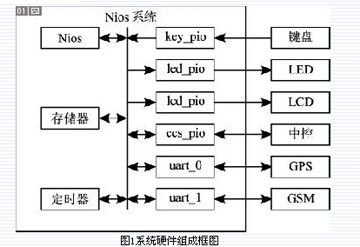

如圖1所示,CPU與外圍設備之間要添加相應的外圍接口,通過Avalon總線與相關部件相連,通過Avalon的讀寫時序對各個設備進行操作。在SOPCBuilder中可以提供眾多IP核,通過定制即可完成相應系統的設計。

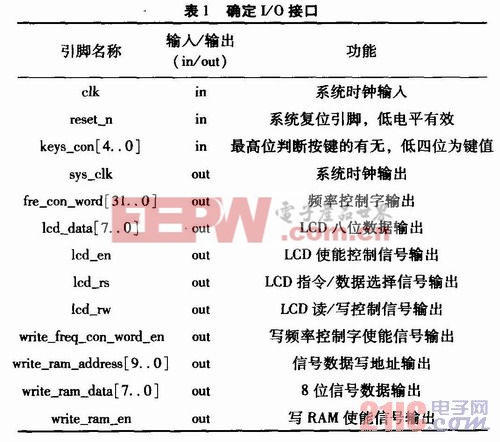

在軟核定制過程中,I/O接口設計充分體現了軟核設計的可裁減優勢,根據系統設計的要求,任意改變IO口的個數和類型,使用方便。根據本設計功能的要求,確定IO口如表1所示。

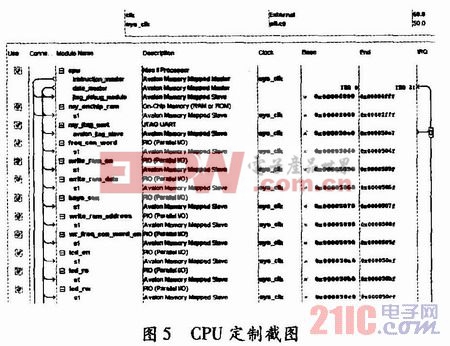

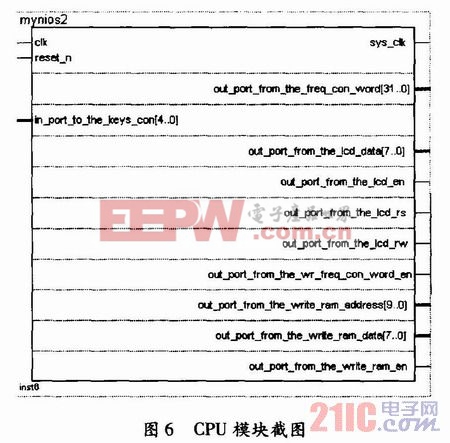

為了使該基本信號產生器系統更加簡化,沒有擴展Flash存儲器以及SRAM存儲器,而采用EPCS1和FPGA內的RAM來代替。EP1C6Q240C8的RAM容量為92 160 bit,在配置時分配空間的大小因程序的大小而定,做到資源的充分合理應用。根據以上分析需要加入的組件有:NiosII CPU Core(CPU核)、片上存儲器以及PIO。配置完成后將會生成如圖5所示定制的CPU配置表。點擊Generate生成模塊,其模塊如圖6所示。

評論