一種基于FPGA核系統的智能429-422信號轉換模塊的設

2.1.1 串行總線控制邏輯設計

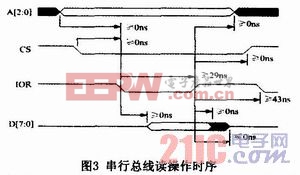

為了將用戶自定制的串行總線控制邏輯接入NiosⅡ系統,必須將其掛入Avalon總線。串行總線控制邏輯在設計上必須實現兩類端口:一類為Avalon總線端口,Avalon總線時序由NiosⅡ系統實現,用戶在邏輯設計時可暫不作考慮;另一類為串行總線控制端口。串行總線讀操作時序如圖3所示,圖中給出了操作時各信號的時序保持關系。本文引用地址:http://www.104case.com/article/191238.htm

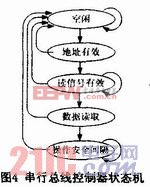

讀時序在設計上可以抽象為一個有限狀態機,如圖4所示。其工作流程為:無數據傳輸時,狀態機停留在空閑狀態;若有數據操作請求時,進入“地址有效”的狀態;再進入“讀信號有效”狀態,依次完成“數據讀取”、“操作安全間隔”狀態(FPGA片外器件要求的兩次操作之間的最小間隔)。考慮到異常產生后狀態機的穩定性,每個狀態都可以在異常產生時返回到默認的“空閑”狀態。同時,有些狀態作了些等待延時,是為了讓控制邏輯與FPGA外部較慢速的器件進行時序匹配。串行總線寫操作時序與讀操作時序相類似。

評論