基于Cyclone III FPGA的DDR2接口設計分析

DDR SDRAM是Double Data Rate SDRAM的縮寫,即雙倍速率同步動態隨機存儲器。DDR內存是在SDRAM內存基礎上發展而來的,能夠在時鐘的上升沿和下降沿各傳輸一次數據,可以在與SDRAM相同的總線時鐘頻率下達到更高的數據傳輸率。雖然DDR2和DDR一樣,都采用相同采樣方式進行數據傳輸,但DDR2擁有兩倍于DDR的預讀取系統命令數據的能力。也就是說,在同樣100MHz的工作頻率下,DDR的實際頻率為200MHz,而DDR2則可以達到400MHz。DDR2還引入了三項新的技術,它們是OCD、ODT和Post CAS。

我們的設計(圖1)采用Altera公司Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產的型號為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成對4片DDR2的控制(帶寬為64bit),且DDR2的最高速率可達200MHz,以此完成對數據的高速大容量存儲。由于采用一個DDR2的IP核進行控制,所以4片DDR2以地址和控制線共用、數據線獨立的方式進行管腳連接。

圖1 接口總框圖

EP3C16只有TOP和BOTTOM邊的BANK支持200MHz DDR2接口(因為DDR2管腳的特殊要求,DQS、DQ、DM管腳在FPGA上都需要專用管腳),且最高速率可達200MHz。

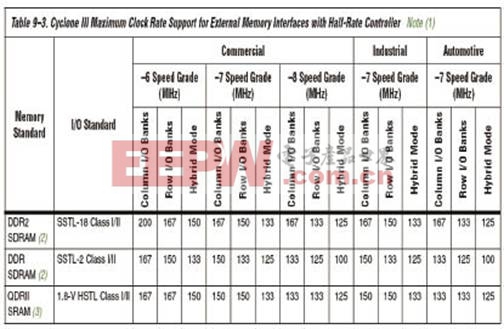

表1中Column I/O是指Top和Bottom I/O,Row I/O是指Right和Left I/O。Hybrid mode是指由Column和Row I/O混合。

從表1中可以看出,Cyclone III只有6系列的FPGA在Top和Bottom BANK才支持200MHz頻率的DDR2。為了滿足設計要求,我們將4片DDR2分別掛在FPGA的Top和Bottom的4個BANK。

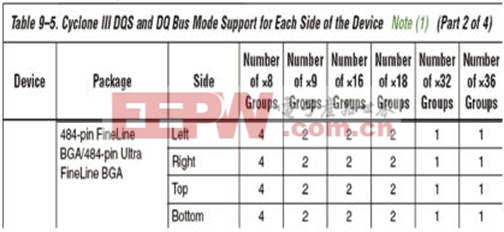

從表2中可以看到,EP3C16 F484封裝系列的FPGA每個邊所支持的DQS和DQ組。因為在DDR中若干個DQ是由一個DQS進行采樣的,所以FPGA以若干個DQ和一個DQS為最小單位進行分組。

表1 FPGA BANK管腳速度

表2 FPGA BANK DQ

如Number of ×8 Groups,其中×8就是指8個DQ,一個DQS即和8個DQ組成一個Group(即這8個DQ由這一個DQS進行采樣)。FPGA分別有Left、Right、Top和Bottom四邊,其表示FPGA的每邊都支持4個DQS和DQ組,而每一邊有兩個Bank,即每個Bank都支持兩個×8架構的DQS和DQ組。圖2展示了FPGA的DQS和DQ組的分配。

由于設計中采用Top和Bottom邊的Bank,這里以第3個Bank的DQS為例進行說明。在圖2可以看到,FPGA的Bank3有三個DQS,分別為DQS1B、DQS3B和DQS5B。由于每組DQ都要和各自對應的DQS配對,所以理論上DQS1B應該和DQ1B為一組,DQS3B應該和DQ3B為一組,DQS5B應該和DQ5B為一組。

評論