基于POWER PC+FPGA架構的飛行試驗振動數據實時分析

(2)功能

POWER PC核心CPU,內置VxWorks實時操作系統,負責系統網絡接口、串行通信接口。Xilinx FPGA芯片,完成自定義FFT頻譜分析及實時信號分析算法。

2.2 實時處理系統軟件設計

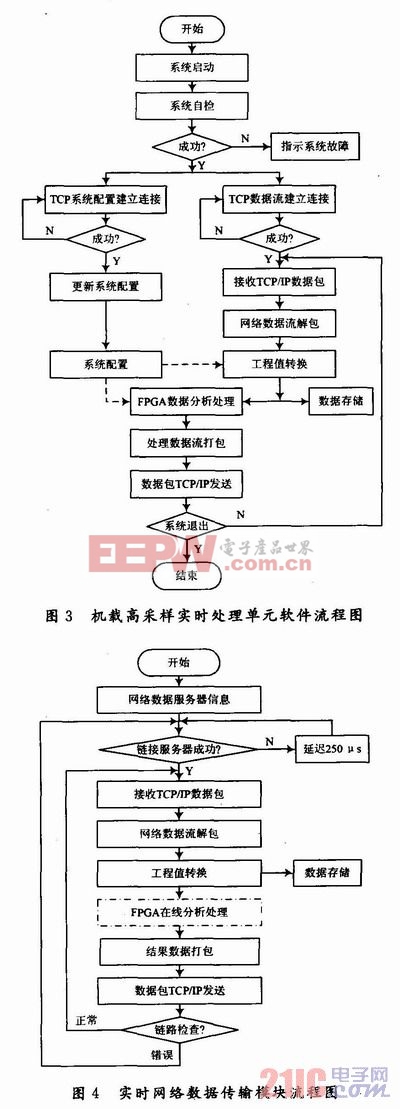

機載振動數據實時處理單元開機后,軟件自動運行,首先完成系統的自檢,判斷系統的工作狀態,如果正常則進行下一步工作,同時將設備面板的“工作正常”指示燈閃爍,反之不閃爍。系統正常后,軟件進入循環連續的數據接收、分析處理與存儲程序,同時處理后的信號發送至機載數據網絡。

高采樣實時處理單元軟件在實時操作系統下運行,使用NI公司的圖形化編程語言LabVIEW RT、高級信號處理包、噪聲振動信號處理包和基于賽靈思公司Xilinx ISE FPGA開發模塊編制完成。機載高采樣實時處理單元配置軟件全部操作采用圖形化的人機界面,能方便、直接、快速完成機載系統的配置。

機載高采樣實時處理單元軟件流程如圖3所示。本文引用地址:http://www.104case.com/article/191225.htm

評論