基于DDS技術三相功率可控PWM信號的FPGA實現

2 設計的測試與結果分析

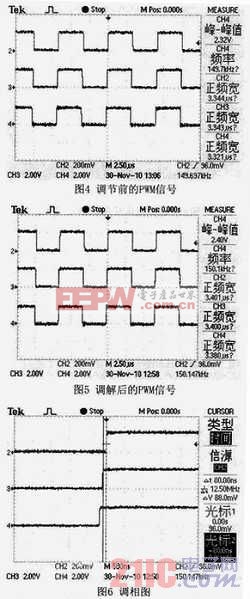

系統的測試結果如圖4、圖5及圖6所示。本文引用地址:http://www.104case.com/article/191205.htm

圖1中的信號為作為比較的基準信號。信號的頻率為149.7kHz,峰峰值2.32V,正頻寬3.344μs,即占空比為50%。信號進行調幅、調頻及調相后如圖5所示,峰峰值為2.40V,步進增量為80mV;頻率調為150.1 kHz,步進增量為0.4kHz;正頻寬3.40 μs,占空比為51%;調相效果如圖6所示,相位調節為2.16°。

測試設備為Tektronix TDS2024型的數字存儲示波器。排除測試過程的誤差,結果調制波形有較高的精度,基本達到了設計要求。

3 結論

基于FPGA實現的DDS的方法結合了FPGA及DDS的特點和優勢,非常適用于產生頻率、相位、占空比可調的信號,這恰好是PWM信號所需求的。目標系統實現了高精度、高分辨率的任意頻率的三相PWM信號發生器的設計,在實測中取得了較好的效果。

pwm相關文章:pwm原理

評論