基于DDS技術三相功率可控PWM信號的FPGA實現

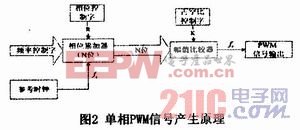

本設計的單相PWM信號在FPGA上實現的原理和過程如圖2所示。相位控制字R設置相位累加器的初始值,可決定PWM信號的初相。圖2中,使用一個幅值比較器取代了圖1中的波形儲存器,幅值比較器是一個0/1輸出的二值比較器,它決定了輸出脈沖的波形。由前面分析可知,累加器的輸出值是線性的,它的值與相位一一對應,因此累加器的輸出值與參數K進行比較結果決定輸出信號fo的高低電平。K作為一個門限值,通過設置K便可設置輸出脈沖波形的占空比,我們把K稱為占空比控制字。多路單相PWM電路共用一個參考時鐘fc就可以構成多相PWM信號,各相PWM均有獨立的R和K,通過設置便可獲得多路同頻異相、占空比不同的PWM信號。本文引用地址:http://www.104case.com/article/191205.htm

由于使用了DDS原理方法,上述PWM脈沖信號具有高頻率和相位分辨率的特點。但圖2中的DDS方法是有區別于傳統DDS實現的,它沒有使用波形存儲單元,節省了FPGA的存儲空間,使設計全數字化,便于在FPGA上實現,方法簡單高效。

1.3 功率可控的設計

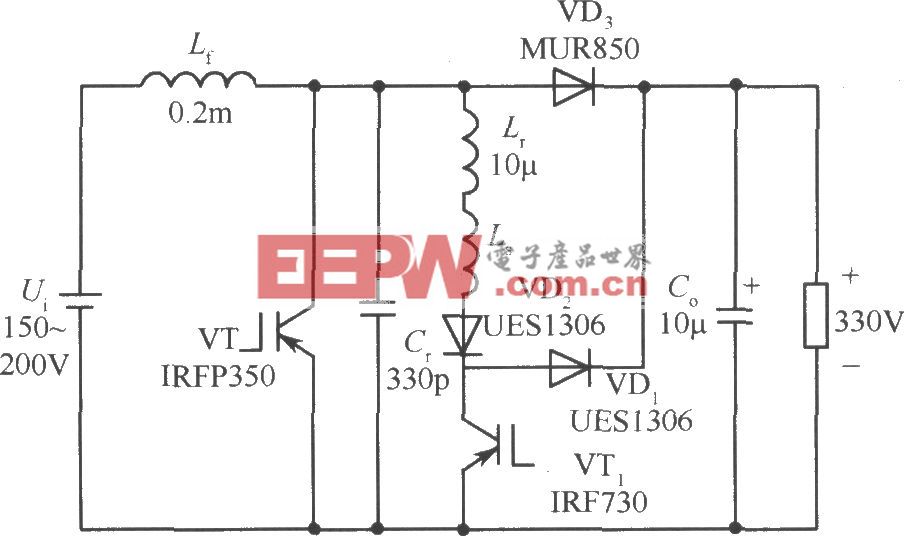

PWM信號的功率可控是為了滿足不同應用的需求。本設計通過程控放大(AGC)實現PWM信號的功率可控,圖3是功率可控的原理框圖。

AD603是美國AD公司繼AD600后推出的寬頻帶、低噪聲、低畸變、高增益精度的壓控VGA芯片。由FPGA、D/A轉換器和可編程增益放大器AD603構成程控放大的原理如圖3所示。FPGA通過對控制D/A輸出直流電壓來控制AD603的內部電阻衰減網絡,實現增益調節。其外圍元件少,電路簡單,由于AD603帶寬最大能達到90MHz,增益范圍有40dB,增益精度在±0.5dB,可精確實現電壓的控制,實現功率的精確步進控制。

pwm相關文章:pwm原理

評論