3.2 模塊設計

3.2.1 分頻模塊

由于SPI總線協議要求的SCK時鐘頻率與FPGA時鐘頻率不一致,所以對基帶時鐘進行分頻。本文中,基帶時鐘頻率為40 MHz,SPI總線時鐘頻率為1 MHz,故需要進行40倍分頻。

3.2.2 發送數據模塊

在片選信號拉低之前,時鐘信必須為低電平。當片選信號拉低后,SCK開始工作,然后寫八位地址,接著寫32位數據;發送操作結束后,片選信號拉高,SCK=0。代碼如下:

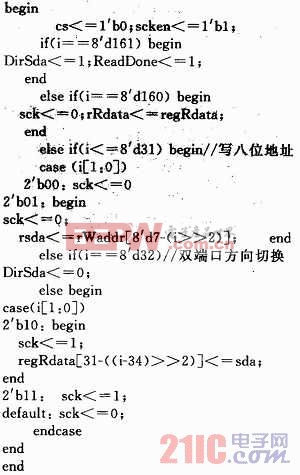

3.2.3 接收數據模塊

當片選拉低后,SCK=0,同時寫八位地址并且使SDA為高阻,再讀32位數據;當片選拉高時,CS=1,SCK=0,此外,在片選信號拉低之前,SCK必須為低電平。代碼如下:

評論