基于FPGA的二值圖像連通域快速標記

3 FPGA實驗結果

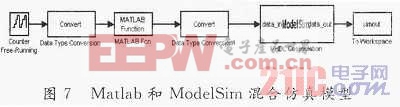

為了能夠仿真該算法的硬件可實現性和正確性,利用Matlab 7.1和ModelSim 6.5a進行混合仿真。通過利用Simulink中Link for ModelSim模塊建立Matlab和ModelSim混合仿真的VHDL協同仿真模型,如圖7所示。

通過Matlab讀入1幅128×128的二值圖像,經VHDL Cosimulation處理后,存到Matlab的工作窗口。然后,通過Matlab把圖像數據還原成圖像矩陣顯示出來,仿真結果如圖8所示。采用XIUNX的ML506開發板對本文的算法進行了驗證,在33 MHz工作時鐘下,單片FPGA能完成1 000 f/s的128×128的二值圖像標記。實驗結果表明本文提出的適于FPGA實現的二值圖像連通域快速標記算法能滿足實時性要求。

4 結語

圖像連通域標記是目標跟蹤與識別圖像處理系統中的重要環節。由于圖像的數據運算量大,利用軟件來實現難以滿足系統的實時性。本文介紹的適于FPGA實現的連通域快速標記算法能夠對二值圖像以自然數順序對圖像連通區域進行快速標記。軟件仿真和硬件實現結果表明,本文介紹的連通域快速標記算法能夠對存在復雜連通關系的二值圖像進行正確標記。該設計只采用單片FPGA實現,電路結構簡單,大大節約了硬件資源,體積小,易于實現。對于較大的圖像的連通域快速標記,只需在FPGA外接存儲器就能夠實現。

評論