基于FPGA的CAN總線控制器設(shè)計(jì)

2 系統(tǒng)驗(yàn)證

整個(gè)系統(tǒng)的功能仿真和時(shí)序仿真是借助Modelsim軟件完成的。圖4所示是對控制器發(fā)送數(shù)據(jù)的驗(yàn)證,測試用的發(fā)送數(shù)據(jù)為隨意選擇的:00101001,仲裁場和控制場也是任選的,分別為:110100101110、110001,設(shè)置好寄存器組后,控制器計(jì)算出對應(yīng)的CRC碼為:110111001111 011,之后控制器將數(shù)據(jù)按CAN協(xié)議的幀格式打包逐位發(fā)送出去。本文引用地址:http://www.104case.com/article/191153.htm

控制器最初處于總線脫離模式,復(fù)位結(jié)束后進(jìn)入總線啟動模式,當(dāng)控制器檢測到總線上的1次連續(xù)11個(gè)隱性位時(shí),進(jìn)入總線空閑模式,接著當(dāng)控制器檢測到總線出現(xiàn)第一個(gè)顯性位時(shí),進(jìn)入模式選擇模式,在此模式下,控制器進(jìn)行的操作就是總線仲裁,確定本節(jié)點(diǎn)是否獲得總線控制權(quán),由于本測試采用的是控制器自測模式,即輸出線與輸入線連在一起,所以仲裁時(shí)間為12個(gè)位時(shí)間,仲裁成功后,控制器會進(jìn)入發(fā)送模式,若無錯(cuò)誤產(chǎn)生,數(shù)據(jù)發(fā)送完成后控制器進(jìn)入間歇模式,最后進(jìn)入總線空閑模式。

經(jīng)過一系列的測試驗(yàn)證后,表明本CAN總線控制器能夠發(fā)送或接收所有符合CAN2.0A協(xié)議的報(bào)文幀。

3 結(jié)束語

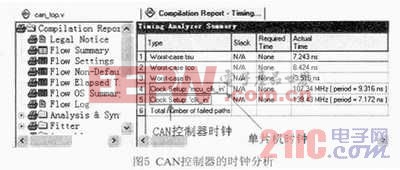

本設(shè)計(jì)實(shí)現(xiàn)了所有符合CAN2.0A協(xié)議的CAN總線控制器功能,最高工作頻率為139.43MHz,這也達(dá)到了最初的設(shè)計(jì)目的。控制器的時(shí)序分析如圖5所示。

本文作者創(chuàng)新點(diǎn)為:首先控制器的外圍接口采用Avalon總線接口,這使得本設(shè)計(jì)的通用性更強(qiáng):其次是本設(shè)計(jì)的最高工作頻率達(dá)到了139.43MHz,能夠適應(yīng)高速通信的要求。

評論