Leon3軟核的FPGA SelectMap接口配置設計

該配置邏輯模塊完成以下幾方面的功能:啟動FPGA1配置時序;向FPGA1內部傳入配置數據;監測FPGA1是否正常配置。使用嵌入式CPU軟核配置FPGA1的流程如下:

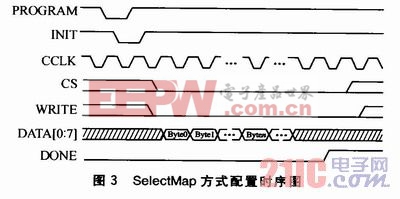

①啟動FPGA1的配置時序。CPU地址線選中FPGA2內部編程寄存器,數據線輸出FPGA1配置控制信號CS、WRITE和PROGRAM,將CS和WRITE置低,PROGRAM置高。

②監測FPGA的配置狀態。CPU地址線選中FPGA2內部輸入寄存器,接收FPGA1的輸出信號INIT,若其值為高,那么CPU開始發出FPGA1的配置數據,否則持續檢查INIT的值,直到其值為1。

③向FPGA1內傳送配置數據。CPU地址線選中FPGA2內部配置寄存器,數據線Data[15:8]輸出FPGA1的配置數據,Data[0]產生配置時鐘CCLK,在CCLK的上升沿FPGA1接收配置數據。配置數據傳送分兩步,首先Data[0]置0,然后Data[0]置1。CCLK產生一個上升沿,在此過程中Data[15:8]數據保持不變。重復此過程,CPU輸出FPGA1全部配置數據。

④檢查FPGA1是否配置成功。FPGA1的配置數據被傳送至結束時,CPU地址線選中FPGA2內部輸入寄存器,接收FPGA1的輸出信號DONE。若其值為高時,說明FPGA1配置成功,否則需要重新配置FPGA1。

SelectMap接口配置方式下FPGA的時序如圖3所示。本文引用地址:http://www.104case.com/article/191145.htm

3 仿真及分析

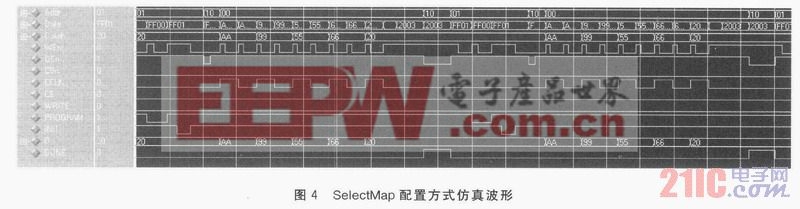

FPGA2采用Xilinx公司的Virtex-5 XC5VFX70T,SelectMap接口控制IP核采用VHDL語言實現,嵌入式CPU軟核采用的是歐空局開發的Lcon3軟核。在XilinxISE 10.1平臺下完成對Lcon3 CPU軟核處理器、外圍控制器及自定義SelectMap接口控制IP核集成的設計、綜合,利用Modelsim SE6.0完成仿真。

SelectMap配置仿真波形如圖4所示。由于FPGA1(Virtex-5 XC5VSX95T)的配置數據較大,仿真出完整的配置過程是不現實的,圖中用5個字節的配置數據來代替FPGA的完整配置過程。為了把配置寄存器數據Data和并行配置的8位數據相對照,分離出了Data的高8位Data[15:8]。從圖中可以看出,在一次完整的配置過程中,CS和WRITE為低,PROGRAM為高,當監測到INIT為高時發出配置數據,在配置時鐘CCLK的上升沿接收8位配置數據,DONE信號為高電平指示配置完成。該仿真結果和SelectMap配置方式的FPGA時序一致,證明了本設計的正確性及可行性。

結語

通過使用嵌入式Lcon3 CPU軟核和FPGA及開發板上的存儲器件,實現了對Xilinx公司的FPGA進行SelectMap配置的一種有效的方案。這種方法減少了外圍器件的數目,增加了硬件系統地靈活性。此外,該方法除了可以完成FPGA芯片的配置外,更重要的是可以靈活地在線升級系統、修改和調試FPGA程序。如果存儲空間夠大,可以存儲不同功能的FPGA程序代碼,這樣就可根據實際情況來加載不同代碼,甚至通過通信接口也可以方便地實現遠程下載代碼和更新系統,使整個系統可在線配置,增強了系統的適用性和靈活性。

評論