Leon3軟核的FPGA SelectMap接口配置設計

2.2 SelectMap接口配置硬件設計實現

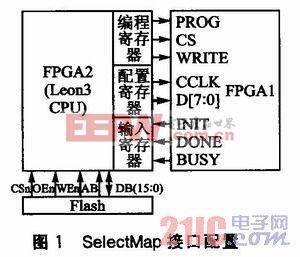

本文設計的SelectMap接口配置系統由兩片FPGA和存儲器(Flash)構成,如圖1所示。設計中FPGA1選用了Xilinx公司Virtex系列芯片Vir-tex-5 XC5VSX95T,是需要進行配置的芯片。FPGA2內部嵌入了Leon3 CPU軟核,可利用該CPU軟核的存儲控制器模塊對Flash進行讀寫控制;利用FPGA內部豐富的資源,在FPGA2內部集成一個自定義的SelectMap接口控制IP核,主要用來產生FPGA的配置信號,這些SelectMap配置信號的狀態由嵌入在FPGA2內部的CPU Leon3軟核監控。該設計采用開源的Leon3軟核CPU,并且充分利用了FPGA豐富的資源,與通常的SelectMap配置系統相比,設計成本低,設計較靈活。本文引用地址:http://www.104case.com/article/191145.htm

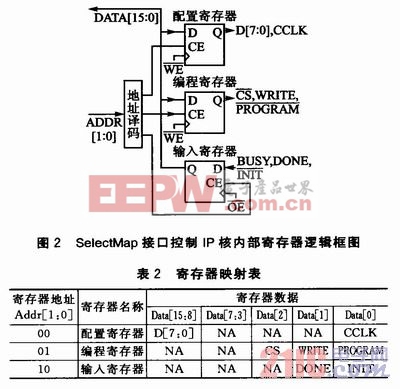

Flash存儲器采用Intel公司的JS28F256P30T95,具有32 MB的存儲空間,用來存儲FPGA1的配置數據。因為Flash的每個地址空間中存儲著16位數據,Leon3 CPU處理器讀取Flash地址中的數據,然后把數據以字節形式傳送到FPGA2。這個過程中,CPU處理器所在的FPGA2為FPGA1提供配置時序控制信號。這些控制信號的產生由FPGA2內部集成的SelectMap接口控制IP核實現。該IP核的功能模塊由3個寄存器組成:配置寄存器、編程寄存器和輸入寄存器。每次CPU對Flash進行讀或寫操作時,這些寄存器存儲FPGA1的配置信號數據。其中配置寄存器和編程寄存器為只寫寄存器,輸入寄存器為只讀寄存器。詳細的邏輯框圖如圖2所示。CPU數據線在SelectMap接口控制IP核內部寄存器的構成如表2所列。

評論