基于CPLD/FPGA的USB讀寫控制器

2 CPLD中的讀寫控制電路

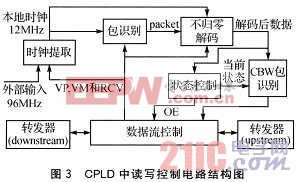

CPLD中的讀寫控制電路包括時鐘提取、包識別、不歸零解碼、狀態控制、CBW包識別和數據流控制等模塊,如圖3所示。時鐘提取部分見參考文獻,包識別和不歸零解碼部分見參考文獻。下面詳細介紹狀態控制、CBW包識別和數據流控制3個模塊。本文引用地址:http://www.104case.com/article/191139.htm

2.1 狀態控制模塊

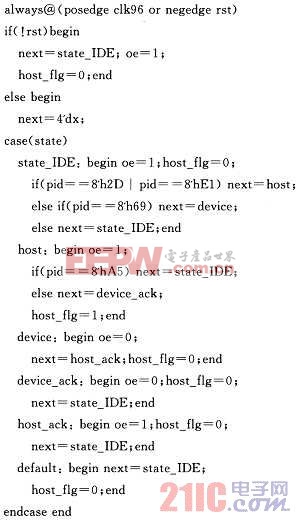

因為IJSB總線是半雙工的,所以CPLD要控制總線數據的方向,即通過OE信號來控制TUSB1106是接收總線數據還是驅動總線。總線上所有的傳輸事務都始于令牌包。令牌包由主機發送,指明本次事務處理過程的含義,包括數據的傳輸方向、設備的地址及端點號等信息。

在本模塊中,通過對PID的檢測可得到每個包的種類,控制狀態機在初始狀態、主機發送數據、設備發送數據、主機發送握手包和設備發送握手包等幾個狀態間跳轉,從而控制其他模塊的狀態。下面為狀態機的部分代碼:

評論