FPGA控制下面陣CCD時序發生器設計及硬件實現

在CCD時序發生器模塊中,輸入為時鐘和復位信號,以及兩路同步信號VD和HD;輸出除了CCD驅動所需的10路信號外,還包括SHP和SHD兩路用于相關雙采樣的電路以及暗像元、啞像元驅動時序。

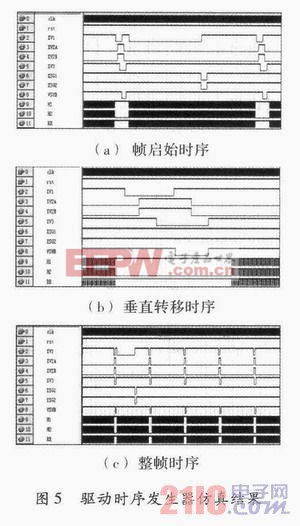

在對VHDL語言描述的時序發生器進行編譯后,對驅動時序發生器進行功能仿真,仿真結果如圖5所示。本文引用地址:http://www.104case.com/article/191097.htm

通過對FPGA芯片程序的下載。將功能模塊集成于CycloneII系列芯片EP2C8T144C8N中。該時序發生器頂層模塊程序資源占用率僅為3%。

4 硬件實現以及測試結果

CCD信號采集驅動電路硬件部分主要分為兩個部分,即CCD驅動電路和偏置電壓的設計。

4.1 偏置電壓電路

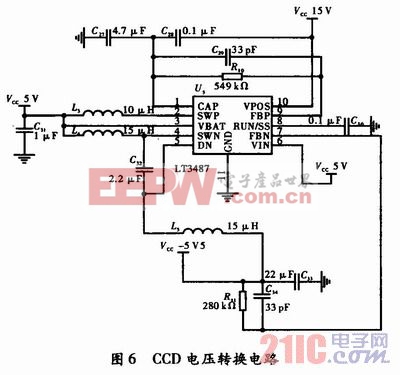

對ICX098BQ的數據手冊進行分析,Hφ1、Hφ2水平移位驅動工作電壓峰峰值為3.3 V,分別為-3.3~0 V和0~3.3 V,Vφ1、Vφ3垂直轉移工作電壓為5.5 V(-5.5~0 V),Vφ2A、Vφ2B為三電平,工作電壓為(-5.5 V、0 V、+15 V)。因而需要-5.5 V和+15 V作為CCD垂直驅動時序的工作電壓。偏置電壓+15 V和-5.5 V采用Linear公司生產的LDOLT3487獲得,偏置電壓產生電路如圖6所示。

評論