FPGA控制下面陣CCD時(shí)序發(fā)生器設(shè)計(jì)及硬件實(shí)現(xiàn)

2.2 驅(qū)動(dòng)時(shí)序分析

ICX098BQ芯片的一個(gè)工作周期分為4個(gè)階段:感光階段、垂直轉(zhuǎn)移階段、幀轉(zhuǎn)移階段和水平讀出階段。感光階段進(jìn)行光電轉(zhuǎn)換,完成感光陣列的電荷積累。垂直轉(zhuǎn)移階段實(shí)現(xiàn)感光陣列積累的電荷包讀出轉(zhuǎn)移到相鄰的垂直移位寄存器。幀轉(zhuǎn)移和水平讀出階段包括電荷包從垂直移位寄存器向水平移位寄存器并行轉(zhuǎn)移以及從水平移位寄存器向輸出放大器的串行輸出。

在CCD工作周期中,首先在Vφ1、Vφ2A、Vφ2B、Vφ3的控制下,感光陣列的垂直移位寄存器進(jìn)行一次電荷轉(zhuǎn)移,將之前殘留下來的電荷徹底清除,為下一步做好準(zhǔn)備。然后垂直驅(qū)動(dòng)時(shí)鐘V1將持續(xù)一段高電平。此刻,讀出時(shí)鐘V2A、V2B跳變?yōu)?15 V的高電平窄脈沖,讀出時(shí)鐘迅速將感光陣列中的所有像素電荷并行地轉(zhuǎn)移到相鄰的垂直移位寄存器中。在每個(gè)行消隱期間,垂直移位寄存器中的電荷在四相垂直驅(qū)動(dòng)時(shí)鐘Vφ1、Vφ2A、Vφ2B、Vφ3交替作用下逐行地向水平寄存器轉(zhuǎn)移。此時(shí)水平驅(qū)動(dòng)時(shí)鐘Hφ、Hφ2保持不變。在行正程期間,轉(zhuǎn)移到水平寄存器的一行信號(hào)電荷受頻率為10 MHz的兩相水平驅(qū)動(dòng)時(shí)鐘Hφ1、Hφ2控制,向浮置擴(kuò)散放大器水平轉(zhuǎn)移。輸出放大器以復(fù)位門時(shí)鐘RG的頻率將像素電荷逐一轉(zhuǎn)換成信號(hào)電壓后串行輸出,在輸出端得到與光學(xué)圖像對(duì)應(yīng)的一行的視頻信號(hào)。

3 基于VHDL的時(shí)序發(fā)生器設(shè)計(jì)

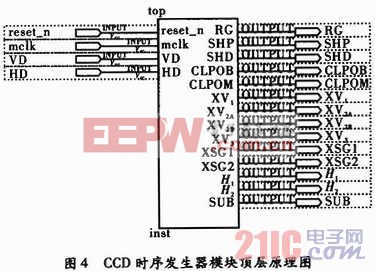

由于面陣CCD驅(qū)動(dòng)時(shí)序的復(fù)雜性,選用硬件描述語(yǔ)言VHDL設(shè)計(jì)CCD時(shí)序。VHDL采用自頂向下的設(shè)計(jì)方式,具有較強(qiáng)的硬件描述能力和仿真能力。在程序中,定義的輸入輸出端包括兩個(gè)輸入端和10個(gè)輸出端。

整個(gè)驅(qū)動(dòng)時(shí)序發(fā)生器的實(shí)現(xiàn)程序?yàn)閮芍厍短椎难h(huán),整個(gè)過程采用3段式狀態(tài)機(jī)來完成。一個(gè)CCD工作周期流程如下:

(1)對(duì)水平寄存器進(jìn)行清空復(fù)位。

(2)垂直轉(zhuǎn)移,將電荷從感光區(qū)轉(zhuǎn)移到相鄰的垂直移位寄存器。

(3)進(jìn)行幀轉(zhuǎn)移和水平讀出階段。幀轉(zhuǎn)移一行,水平讀出一行,直到整幀讀出完畢。

(4)返回,讀取下一幀。即返回步驟(1)。

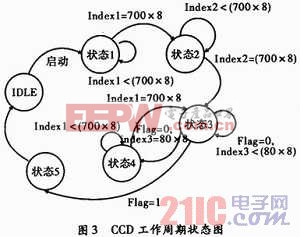

狀態(tài)轉(zhuǎn)移圖如圖3所示。本文引用地址:http://www.104case.com/article/191097.htm

IDLE:為空閑狀態(tài);當(dāng)積分啟動(dòng)后,轉(zhuǎn)到狀態(tài)1。

狀態(tài)1:為預(yù)讀出狀態(tài);讀出水平寄存器內(nèi)的電荷,當(dāng)水平讀出700個(gè)電荷后,轉(zhuǎn)向狀態(tài)2,否則,自循環(huán)。

狀態(tài)2:為垂直轉(zhuǎn)移狀態(tài);使感光區(qū)的電荷轉(zhuǎn)移到垂直移位寄存器,垂直轉(zhuǎn)移后,轉(zhuǎn)到狀態(tài)3。

狀態(tài)3:幀轉(zhuǎn)移狀態(tài);其中Flag為場(chǎng)有效標(biāo)志,當(dāng)Flag=1時(shí),進(jìn)入積分狀態(tài),開始下一幀的工作。

狀態(tài)4:水平讀出狀態(tài)。

狀態(tài)5:積分狀態(tài),轉(zhuǎn)向空閑狀態(tài),開始下一幀的工作。

根據(jù)分析,設(shè)計(jì)出產(chǎn)生上述時(shí)序的頂層原理圖,如圖4所示。

評(píng)論