Xilinx FPGA抗輻射設計技術研究

摘要:針對Xilinx FPGA在航天應用中的可行性,文章分析了Xilinx FPGA的結構以及空間輻射效應對FPGA的影響,結合實際工程實踐給出了提高其可靠性的一有用辦法和注意事項,如冗余設計、同步設計、自檢等。表明配置信息的周期刷新和三模冗余設計是減輕單粒子效應的有效方法。

關鍵詞:可編程邏輯門陣列;總劑量效應;單粒子翻轉;單粒子閂鎖;單粒子功能中斷;單粒子燒毀:單粒子瞬

0 引言

空間輻射環境中的帶電粒子會導致航天器電子系統的半導體器件發生單粒子效應,嚴重影響航天器的可靠性和壽命,其中高能質子和重離子是導致單粒子效應的主要因素。必須對航天器用電子元器件的單粒子效應進行評估,采取一定的抗輻射加固措施,提高其可靠性。因此,空間輻射的單粒子效應研究具有重要意義。

基于SRAM的FPGA在航天領域受到極大關注。Xilinx公司的FPGA相繼在MARS2003 Lander(JPL)XQR4062XL:Controlling Pyrotechnics、MARS2003 Rover(JPL)XQVR1000:Motor Control、GRACE(NASA、XQR4036XL:Sensor等任務中成功應用之后,國外航天界對Xilinx FPGA的應用興趣大增。我國相關領域對XilinxFPGA的航天應用正處在研究階段,對其中亟待解決的可靠性設計問題研究相對較少,本文根據作者在某衛星載荷設備信號處理器中的實踐對Xilinx FPGA(以下簡稱FPGA)的可靠性設計技術進行了研究。

1 Xilinx FPGA介紹

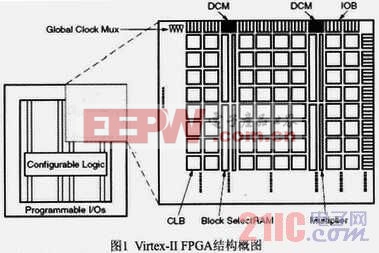

Xilinx SRAM型FPGA主要由以下幾部份組成,圖1所示為Virtex II FPGA的結構圖。

(1)配置存儲器(Configure Memory):FPGA可以看作配置存儲器和受其控制的可配置邏輯資源兩層的疊加。配置存儲器是FPGA內部的一個大容量存儲器,控制著可配置邏輯資源,如布線資源、可編程邏輯資源、數字時鐘等邏輯功能。配置存儲器的失效將造成FPGA功能的持久失效(直至重新配置成功)。

(2)布線資源(Routing Resource):布線資源是FPGA內部邏輯功能單元互聯的通道,它將用戶設計的各個邏輯功能模塊連在一起。

(3)可編程I/O(Programmable I/O):FPGA的輸入輸出接口,通常情況下I/O腳可以設置成輸入、輸出、高阻態、雙向I/O。

(4)可編程邏輯單元(CLB:Configurable LogicBlock):可編程邏輯功能單元是FPGA的細胞,通過它可以完成各式各樣的邏輯功能。

(5)塊存儲器(Block Select-RAM)和乘法器(Multiplier)等:FPGA內部集成的硬件存儲器和乘法器,用以實現快速的數字運算。

(6)數字時鐘管理模塊(DCM:Digital ClockManager):FPGA內部的時鐘管理單元。通過它可以對輸入時鐘進行倍頻、分頻處理,同時還可以減小時鐘的抖動,提高時鐘的驅動能力。

目前FPGA的工藝水平從Virtex系列的220mm發展到Virtex II的150mm,一直到現在Virtex 4系列高密度FPGA的90nm,雖然抗總劑量效應能力在不斷增強,但是隨著器件的核電壓的降低、門數的劇增,單粒子效應會越來越明顯。因此FPGA上述組成部分,如配置存儲器、CLB和塊存儲器的抗輻射可靠性設計越來越重要。

評論