基于SOPC的雷達多功能接口模塊的設計與實現

2.2 M0子模塊電路設計

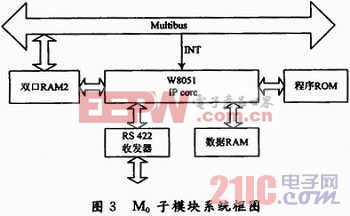

圖3為內總線接口子模塊(M0)系統框圖,W8051是與8051單片機兼容的IP軟核,它通過工作在方式2下的8051串行口實現雷達內總線M0主控器功能,分別為W8051擴展了4 KB的程序ROM和256 B的RAM,同時擴展了4 KB的雙口RAM2并掛接在Multibus上,以實現與主控計算機的數據交換。主控計算機通過一個I/O(INT)來中斷W8051,整個M0控制系統均在FPGA內部實現,軟件在這個獨立的計算機系統上實現自定義的M0內總線通信協議,以完成主控計算機與內總線上雷達其他從設備(如發射機、接收機等)的可靠通訊。本文引用地址:http://www.104case.com/article/191090.htm

2.3 TVJ子模塊電路設計

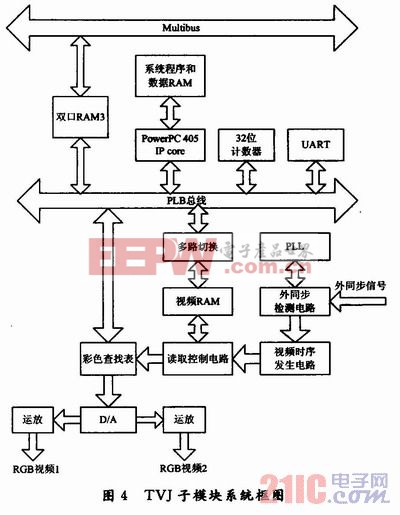

TVJ功能塊的核心是基于FPGA的硬處理器核PowerPC 405,PowerPC 405是專門為嵌入式應用而設計的高性能32位PowerPC系列處理器芯核,對于Virtex-ⅡPro系列FPGA,其實現型號為PowerPC405D5,其內核的結構主要包括1個5級流水線單元,1個虛擬存儲器管理單元,1個指令和數據獨立的Cache單元,1個調試口和3個可編程計數器,片內總線遵循PLB(Processor Local Bus)標準,PLB是一種高性能的同步總線,用于連接處理器和高速外設,提供分離的32位地址總線和64位數據總線。通過PLB總線接口實現對視頻RAM、彩色查找表LUT、32位計數器、UART和雙口RAM3的擴展,在雙口RAM3的另一端實現了與Multibus的存儲器接口及雙向中斷功能,視頻RAM分為A、B兩塊,共4 MB,顯示分辨率為575×575×16 b,通過PLB總線和多路切換電路可以對它們進行讀/寫,同時視頻RAM的內容經讀取控制電路讀出后經彩色查找表變換為24位真彩色數字視頻再經過D/A變換和運放的驅動輸出模擬視頻信號。通過PLB總線可以隨時設置彩色查找表LUT的內容以實時地進行多種分層疊加彩色顯示方式的切換。視頻時序發生電路產生符合PAL制式的同步/消隱信號,當有外部同步信號輸入時,外同步檢測電路可自動識別出來并與外部的鎖相環(PLL)配合,產生與外同步信號完全一致的視頻時序信號,保證最后輸出的模擬視頻與其完全同步。除去視頻RAM,PLL,D/A、和運放電路外,整個PowerPC 405系統和顯示控制的時序、邏輯電路及彩色查找表等都在FPGA內部實現。如圖4所示。

評論