基于軟件測試技術的FPGA測試研究

現場可編程門陣列(FPGA)的出現大大壓縮了電子產品研發的周期和成本,由于FPGA器件具有高密度、低功耗、高速、高可靠性等優點,在航空、航天、通信、工業控制等方面得到了大量應用。隨著FPGA應用領域的擴展以及重要性和復雜程度的提高,其可靠性問題變得越來越突出,因此對FPGA系統的測試需求變得尤為迫切。

目前FPGA測試技術的研究主要集中于對FPGA芯片資源的測試,通過編程覆蓋FPGA所有的邏輯資源[1,2]和連接資源[3],驗證每個單元基本邏輯功能的正確性,而無法對電路的整體行為進行有效的驗證。硬件描述語言(HDL)是FPGA電路設計的主要實現方式,和軟件一樣,HDL也是人腦思維的邏輯產物,同樣存在著不希望或不可接受的人為錯誤。隨著設計復雜程度的提高,由HDL引入的缺陷成為影響FPGA可靠運行的關鍵因素,對FPGA電路行為的測試成為提高系統質量和可靠性的重要環節。

MIN Y.H.提出了在FPGA系統中進行高層測試的必要性[4]。高層測試即任何高于門級的測試,考慮的是高層描述,如HDL、狀態圖、功能塊圖等,通過高層測試發現設計中的缺陷,并在系統的開發階段充分考慮測試需求,指導系統設計。以此為基礎,先后提出了一系列具體的實施方法,如層次化的測試方法、基于電路功能或結構的測試方法、基于模擬的測試方法等。

1 研究背景

1.1 軟件測試技術概述

在IEEE的軟件工程標準術語中,軟件測試定義為使用人工和自動手段來運行或測試某個系統的過程,其目的在于檢驗它是否滿足規定的需求或找出預期結果與實際結果之間的差別。

按照測試級別,軟件測試包括單元測試、部件測試、配置項測試、系統測試等;按照測試方法,軟件測試可分為動態測試和靜態測試,動態測試又可分為黑盒測試和白盒測試。靜態測試包括了代碼審查、靜態分析、代碼走查等測試類型;動態測試包括邏輯測試、功能測試、性能測試、接口測試等測試類型。白盒測試通常采用以邏輯覆蓋衡量的結構性測試技術;黑盒測試通常采用包括功能分解、等價類劃分、邊界值分析等在內的功能性測試技術[5]。

1.2 FPGA系統的特點

FPGA作為可編程邏輯器件,通過編程的方式(如HDL)將通用芯片配置成用戶需要的硬件數字電路,FPGA和軟件系統具有相似的結構和開發方式,HDL與軟件都是人腦思維邏輯的產物,具有相似的語法和失效機理。因此,將軟件測試的成熟技術用于FPGA測試,在理論和操作上均具有可行性。

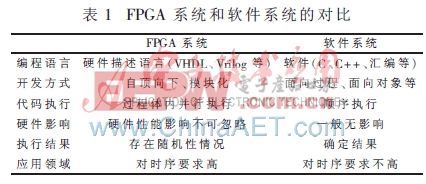

但是,由于軟硬件系統本質上的不同,FPGA和軟件系統在測試要求上存在一定的差異,表1從開發方式、代碼執行順序、受硬件影響程度、執行結果的隨機性以及應用領域等方面,歸納了FPGA和軟件系統的不同之處。

2 FPGA特有測試要求

針對FPGA和軟件系統的差異,存在不同于軟件測試特有的測試要求,包括HDL代碼檢測要求、測試級別要求和時序測試用例設計要求等。

2.1 HDL代碼檢測要求

由于HDL代碼并行執行并存在硬件環境的影響以及競爭、冒險等不確定結果,在白盒測試中具有不同于軟件測試的要求。一方面,不同于軟件的控制流和數據流,并行程序的時序和信號流是一對相互依存的信息,程序的邏輯狀態由二者共同確定。這就要求在測試中,既要依據信號流圖對組合邏輯進行驗證,還要依據時序圖分析時變信號的時序一致性。另一方面,硬件特征對運行結果的影響也是代碼檢測中需要考慮的因素[6]。在編碼規范的制定上,應當充分考慮并行程序的特點,正確處理與硬件資源之間的關系,避免競爭、冒險等不確定結果的產生。

2.2 測試級別的要求

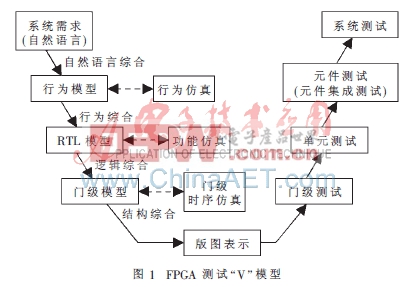

與傳統自底向上的電子設計技術不同,FPGA采用與軟件開發相同的自頂向下的設計方法。一個項目的開發過程,從系統的分解、RTL模型的建立、門級模型的產生,到最終的可以物理布線實現的底層電路,是一個從高抽象級別到低抽象級別的開發周期。在開發過程中,需要在每一階段分別進行行為仿真、功能仿真、門級時序仿真等仿真驗證,而在測試階段需要自底向上依次從門級、元件功能級到系統行為級進行測試。

2.3 時序測試用例設計要求

FPGA的并行運算和高響應速度的特性,使其在對高速時序邏輯的處理中得到廣泛應用。因此對FPGA系統功能、性能的測試中,不能僅僅局限于對穩態輸入輸出的驗證,還需要驗證系統對時序信號的響應及輸出量隨時間變化正確性的判斷。因此在測試用例的設計中,需要對系統輸入、輸出的時間變化趨勢進行規定,并提供動態輸出信號的判斷準則,同時需要開發時序測試環境支持測試用例的執行。

3 FPGA測試技術框架

3.1 測試級別

把抽象的實體結合成單個或統一實體的過程稱為綜合,FPGA系統的每一步開發過程都可以稱為一個綜合環節,即將自然語言表示經過自然語言綜合轉換為HDL算法表示,再通過行為綜合轉換在寄存器傳輸(RTL)級,進一步通過邏輯綜合轉換為邏輯門的表示,最終通過結構綜合轉換為版圖表示。對于每一個綜合環節,都對應響應的測試級別,FPGA測試的“V”模型如圖1所示。

評論