基于FPGA的PCM30/32路系統(tǒng)信號(hào)同步數(shù)字復(fù)接設(shè)計(jì)

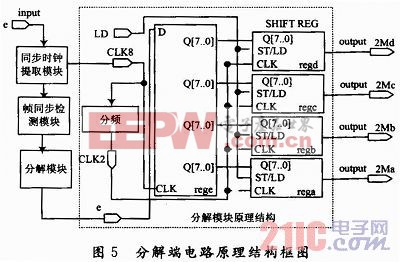

3.3 分解端電路設(shè)計(jì)原理

在分解端,8 MHz高速串行信號(hào)e首先經(jīng)過(guò)同步時(shí)鐘提取模塊,根據(jù)串行數(shù)據(jù)的內(nèi)部特點(diǎn),利用數(shù)字鎖相環(huán)等技術(shù)提取出和發(fā)送端同頻、同相的時(shí)鐘信號(hào)CLK8,然后經(jīng)過(guò)幀同步檢測(cè)模塊,建立狀態(tài)機(jī)對(duì)串行數(shù)據(jù)中的TS0時(shí)隙的幀同步碼元進(jìn)行檢測(cè);這樣保證了接收端能夠準(zhǔn)確無(wú)誤的恢復(fù)發(fā)送端的數(shù)據(jù)。對(duì)于高速數(shù)據(jù)分解為4路支路信號(hào)的電路原理剛好和復(fù)用端相反,如圖5所示。本文引用地址:http://www.104case.com/article/191080.htm

3.4 分解端功能仿真結(jié)果分析

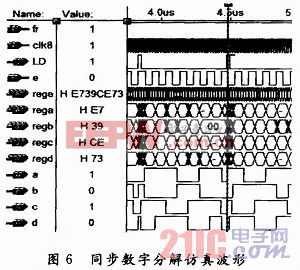

與復(fù)接端相反,利用CLKS高頻時(shí)鐘讀取串行e的碼元信號(hào)到鎖存器rege中,LD信號(hào)為內(nèi)部邏輯產(chǎn)生的控制信號(hào),負(fù)責(zé)碼元分解搬移。由于一幀信號(hào)容量過(guò)大,故截取了某幀內(nèi)的一個(gè)時(shí)隙以便于觀察分解還原功能的實(shí)現(xiàn),在32個(gè)CLK8時(shí)鐘周期內(nèi)從串行輸入數(shù)據(jù)e采集到的碼

元信號(hào)鎖存在rege移位寄存器中,如圖6所示,rege=11100111001110011100111001110011B(E739CE73H),從波形圖上可見分解后的支路鎖存實(shí)時(shí)狀態(tài)值為:rega=111001 11B(E7H);regb=OO11l001B(39H);regc=11001110B(CEH);regd=01110011B(73H),而恢復(fù)出4個(gè)支路的時(shí)隙碼元信號(hào)為:a:11100111;b:00111001;c:11001110;d:01110011。分解過(guò)程及其信號(hào)分解還原波形如圖6所示。

4 結(jié)語(yǔ)

本文主要依據(jù)PCM30/32基群信號(hào)的特點(diǎn),結(jié)合FPGA建模仿真,利用QuartusⅡ8.0仿真綜合軟件,實(shí)現(xiàn)4路低速信號(hào)的同步時(shí)分復(fù)用,提高信號(hào)傳輸效率;并在分解端將其分解還原為4路原始信號(hào)。功能仿真結(jié)果正確,在允許的信號(hào)延時(shí)下實(shí)現(xiàn)了系統(tǒng)主要功能。系統(tǒng)基于FPGA的設(shè)計(jì),便于功能修改和擴(kuò)展,只需實(shí)時(shí)修改內(nèi)部參數(shù)即可。

評(píng)論