基于FPGA控制VGA顯示的多通道數字示波器的設計

2.2 A/D轉換電路

A/D轉換模塊采用存儲采樣數據的并行數據處理方法,這樣可以使硬件電路得到最大程度的簡化,同時也提高了系統的穩定性。AD部分的采樣,選用實時采樣技術。能夠捕獲到單個信號。采樣速率為10 MHz,即在最高頻率1 MHz時,實時采樣可以在每周期采10個點以保證取到一個完整的信號波形。

2.3 觸發電路模塊

觸發電路模塊屬于外觸發,對模擬信號實現任意電平觸發,該模塊采用電壓比較器來實現單次觸發。

2.4 存儲模塊

存儲模塊包括內存儲和外存儲兩部分,使用外部電路進行搭建的為外存儲,內存儲在軟件部分進行說明。

外部非易失性存儲器模塊采用存儲容量為16 KB的E2PROM芯片24C128,該芯片作為手動存儲的存儲介質,從而實現掉電不丟失的設計目的。

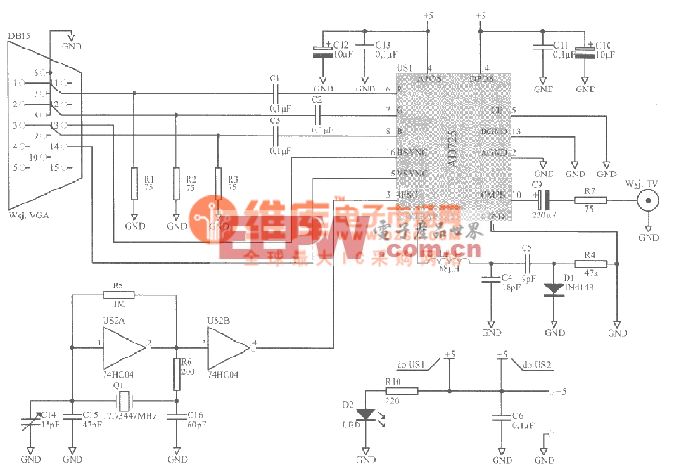

2.5 VGA顯示模塊

VGA顯示模塊是建于FPGA內的雙緩沖機制,由嵌入的MicroBlaze軟核進行控制,能夠進行多個頁面間的切換。另外,每個界面,可以實現中文信息、彩色通道和所測輸入波形的顯示,并可控制顯示內容的顯示顏色。

2.6 鍵盤模塊

4×4矩陣鍵盤模塊實現人機交互。

通過鍵盤,可以對示波器的數字通道、模擬通道、混合通道、存儲、回放、波形左移、波形右移等功能進行選擇。

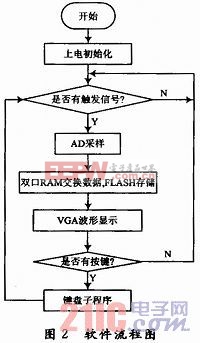

3 基于FPGA的軟件設計

FPGA的硬件主要包括:觸發電路模塊、數字信號發生模塊、存儲模塊、鍵盤模塊、VGA顯示模塊等5個部分,軟件流程圖如圖2所示。本文引用地址:http://www.104case.com/article/191068.htm

3.1 觸發電路程序

AD采樣啟動后,將從AD進來的數據與觸發字進行比較,當滿足設定條件時,會產生觸發信號,此信號送到RAM控制器端。通過對外部觸發電路發出觸發信號與內部的兩路數字信號進行觸發的選擇后,RAM控制器得到觸發后將采樣數據寫入到RAM中。當RAM在進行寫數據過程中觸發信號是被抑制的;當RAM達到預觸發深度時,釋放觸發信號,等待下一次觸發的到來。

3.2 數竽信號發生程序

利用DDS的原理,在FPGA內部生成一個信號發生器。主要包括頻率控制寄存器、高速相位累加器和比較器3部分。具體做法為:使用一個表示信號平均值的數據與AD采樣得來的數據進行比較得到同頻同相的A路信號,再經由A信號觸發計數器,經過合理設置計數脈沖,得到有45°延時,占空比25%的B路信號。最后對該相位值計算數字化正弦波幅度輸出。

表示信號平均值的數據由MicroBlaze測量信號提供。

評論