基于FPGA的外部存儲器設計

2 存儲電路軟件設計

2.1 SDRAM控制器設計

SDRAM具有空間存儲量大、讀/寫速度快、價格相對便宜的特點,因此許多嵌入式設備的大容量、高速度存儲器都采用SDRAM來實現,但其控制邏輯復雜,需要周期性刷新操作、行列管理、不同延時和命令序列等。目前,大多都采用專用芯片完成它的控制電路,這不但提高了設計成本,而且使系統的硬件電路變得復雜。隨著FPGA在嵌入式系統中的廣泛應用,FPGA管腳設計靈活,結合具體的需要,利用FPGA來設計一個滿足雷達信號處理專用的SDRAM控制器,就可以極大地增加設計的靈活性,且硬件規模小,又可以滿足實時信號處理需求。本文就是基于這種處理方法來設計一個SDRAM控制器。

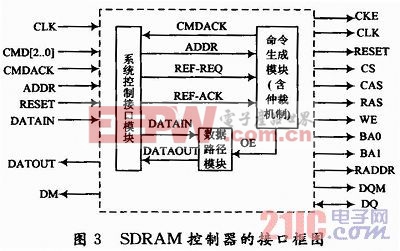

在SDRAM控制器的FPGA實現方案中,采用FPGA的自底向上模塊化設計思想。首先分析頂層模塊所要完成的功能,之后再將其功能分類細化,分配到不同的子模塊去實現,然后從底層向頂層的先逐步完成各個子模塊的設計,最后將子模塊相互連接生成所需的頂層模塊。設計SDRAM控制器是為了更好地滿足SDRAM與FPGA的通信而設計的。下面將具體介紹SDRAM控制器的設計方法。圖3為參考Altera公司SDRAM控制器的而設計的接口框圖。本文引用地址:http://www.104case.com/article/191065.htm

下面對接口信號進行介紹:與主機接口信號有CLK:系統時鐘信號;RESET:系統復位信號;CMD[2:0]:譯碼指令;CMDACK:指令應答信號,通知主機命令已被SDRAM執行;ADDR:地址線,該設計中為22位,A21,A20代表頁地址BA1,BA0;A19~A8代表行地址;A7~A0代表列地址;DATAIN/DATAOUT:輸入、輸出數據總線;DM:數據掩碼。與SDRAM接口信號有RADDR:12位地址線,在讀/寫操作時,地址線時復用為行地址和列地址;BA0,BA1頁地址選擇;CS:片選信號;CKE:時鐘使能信號;RAS,CAS,WE:命令控制信號;DQM:SDRAM數據掩碼;DQ:雙向數據線。SDRAM控制器作為頂層模塊,內部由3個主要模塊構成:系統控制接口模塊、命令生成模塊和數據路徑模塊。系統控制接口模塊用于接收系統的控制信號,進而產生不同的CMD命令組合;命令用于接收CMD命令并解碼成操作指令并產生SDRAM的操作動作;數據通路模塊則用于控制數據的有效輸入/輸出。

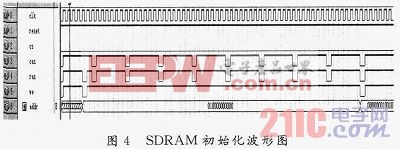

使用SDRAM的目的是進行數據傳輸,即要求能正確地讀寫數據。因此,在SDRAM操作過程中,最重要是就是初始化、讀和寫的操作,因此,本文完成了SDRAM初始化在QuailtusⅡ仿真下的時序波形圖,如圖4所示。

評論