基于FPGA的外部存儲器設計

摘要:為了提高雷達海量數據的處理速度,采用FPGA設計了一種高速外部存儲器,通過多次實驗,驗證了設計方法的可行性。高速外部存儲器可以有效地提高數據存儲速度,節約讀/寫時間,從而滿足信號處理的高速實時的要求。這種方法充分利用FPGA設計方便,SDRAM和FLASH的存儲讀寫速度快的優勢,具有成本低廉,兼容性強,易于工程實現的特點。

關鍵詞:雷達信號處理;FPGA;SDRAM;FLASH;存儲器設計

0 引言

隨著雷達技術的進一步發展,對雷達信號處理的要求越來越高,在實時信號處理過程中有大量數據需要存儲,由于FPGA本身的存儲器容量非常小,根本滿足不了雷達信號處理過程中的需求,為解決這一問題,通過查詢資料,引入SDRAM和FLASH作為FPGA的外部存儲器。SDRAM存儲器以其快速、方便和價格相對便宜,因而,常被用在雷達信號實時處理上。選擇SDRAM而沒有SRAM是因為SRAM價格太貴,SDRAM相對便宜。沒有選擇DDR SDRAM的原因是因為在實際的雷達信號處理中并不需要那么高burst率,SDRAM足以滿足實際需求。SDRAM主要作用:在MTI處理時作為周期延遲器件、動態雜波圖的存儲和數據暫存等功能。雖然SDRAM有存儲容量大、價格相對便宜等優點,但是其斷電所有數據丟失的缺點,使其僅在FPGA外部連接SDRAM作為外部存儲器件顯然是不能滿足設計需求的,因此,在設計過程中考慮到FLASH存儲。在設計中用FLASH存儲一些斷電不能丟失的數據,如:脈沖壓縮處理時的匹配濾波器系數、MTI處理時雜波加權系數、CFAR處理時的對數表以及一些函數求值等。

1 存儲電路設計

1.1 SDRAM存儲電路設計

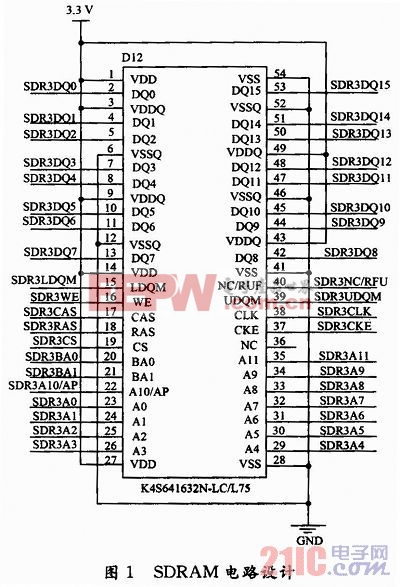

在硬件電路設計過程中,先通過SDRAM的I/O接口電平標準選擇FPGA的外圍I/O電平標準,從而解決電氣互聯問題。根據實時信號處理過程中所需的存儲容量以及FPGA的型號,選擇了4片SDRAM存儲器,用于輸入/輸出緩存。芯片的型號為K4S641632N-LC/L75。SDRAM工作模式有多種,內部操作是一個復雜的狀態機。SDRAM的管腳可以分為以下幾類:控制信號,包括片選、時鐘、時鐘使能、行列地址選擇、讀/寫選擇、數據有效等。地址線行列復用,數據引線是雙向傳輸。SDRAM的所有操作都同步于時鐘,都是在時鐘上升沿時控制管腳和地址輸入的狀態,進而產生多種需要的命令。

SDRAM與FPGA的連接,要把FPGA的普通I/O與SDRAM的除電源、NC和接地管腳之外管腳連接起來即可,所有的控制與工作時序都是由FPGA提供,由于管腳太多,采取了網絡標號連接,其電路原理圖如圖1所示。由于篇幅關系,只給出了部分電路圖。

評論