基于ARM和CPLD的嵌入式視覺系統設計

由圖1可見,微處理器的總線接在CPLD上,在對功耗有嚴格要求的場合中,只需要在CPLD中,將OV6620的同步時序信號所對應的引腳與LPC2214連接在CPLD上的中斷引腳相連,系統就可以轉換成方案1的形式。對CPLD而言,引腳相連的僅僅是組合邏輯,降低了功耗。方案1的具體工作過程可見參考文獻[1]。

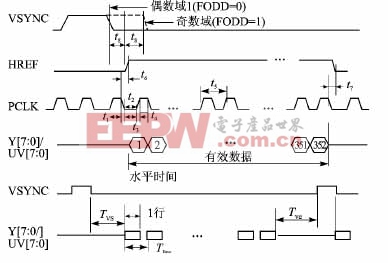

圖2 OV6620輸出時序圖

在Verilog語言中,對上升沿的檢測是通過always語句來實現的。例如檢測時鐘信號cam_pclk的上升沿:

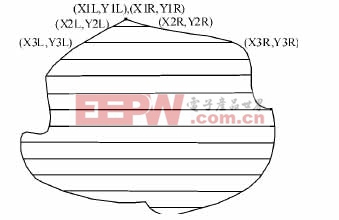

圖3 行處理得到的線形圖

根據得到的結果,可以計算出更多關于跟蹤物體的信息:

① 計算區域面積。計算每條線段的長度l(n),然后將l(n)進行累積疊加,即可獲得跟蹤區域面積值S。![]()

評論