基于ARM和CPLD的嵌入式視覺系統設計

目前,關于視覺系統的研究已經成為熱點,也有開發出的系統可供參考。但這些系統大多是基于PC機的,由于算法和硬件結構的復雜性而使其在小型嵌入式系統中的應用受到了限制。上述系統將圖像數據采集后,視覺處理算法是在PC機上實現的。隨著嵌入式微處理器技術的進步,32位ARM處理器系統擁有很高的運算速度和很強的信號處理能力,可以作為視覺系統的處理器,代替PC機來實現簡單的視覺處理算法。下面介紹一種基于ARM和CPLD的嵌入式視覺系統,希望能分享嵌入式視覺開發過程中的一些經驗。

本文引用地址:http://www.104case.com/article/191055.htm1 系統方案與原理

在嵌入式視覺的設計中,目前主流的有以下2種方案:

方案1圖像傳感器+微處理器(ARM或DSP)+SRAM

方案2圖像傳感器+CPLD/FPGA+微處理器+SRAM

方案1系統結構緊湊,功耗低。在圖像采集時,圖像傳感器輸出的同步時序信號的識別需要借助ARM的中斷,而中斷處理時,微處理器需要完成程序跳轉、保存上下文等工作[1],降低了圖像采集的速度,適合對采集速度要求不高、功耗低的場合。

方案2借助CPLD來識別圖像傳感器的同步時序信號,不必經過微處理器的中斷,因而系統的采集速度提高,但CPLD的介入會使系統的功耗提高。

為了綜合以上2種方案的優勢,在硬件上采用“ARM+CPLD+圖像傳感器+SRAM”。該方案充分利用了CPLD的可編程性,通過軟件編程來兼有方案1的優勢,具體體現在以下方面:

① 功耗的高低可以控制。對于功耗有嚴格要求的場合,通過CPLD的可編程性將時序部分的接口與ARM的中斷端口相連,僅僅是組合邏輯的總線相連,可以降低CPLD的功耗從而達到方案1的效果;對于采集速度要求高而功耗要求不高的情況,可以充分發揮CPLD的優勢,利用組合與時序邏輯來實現圖像傳感器輸出同步信號的識別,并將圖像數據寫入SRAM中。

② 器件的選擇可以多樣。在硬件設計上,所有總線均與CPLD相連;在軟件設計上,不同的模塊單獨按功能封裝。這樣以CPLD為中心,系統的其他器件均可更換而無需對CPLD部分程序進行改動,有利于系統的功能升級。

作為本系統的一種應用,開發了視覺跟蹤的程序,可以在目標和背景顏色對比強烈的情況下對物體進行跟蹤。通過對CMOS攝像頭采集來的數據進行實時處理,根據物體的顏色計算出被追蹤物體的質心坐標。下面分別描述系統各部分的功能。

2 系統硬件

2.1 硬件組成及連接

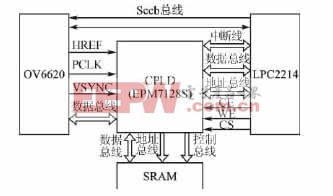

系統的硬件主要有4部分:CMOS圖像傳感器OV6620、可編程器件CPLD、512 KB的SRAM和32位微處理器LPC2214。

OV6620是美國OmniVision公司生產的CMOS圖像傳感器,以其高性能、低功耗適合應用在嵌入式圖像采集系統中,本系統圖像數據的輸入都是通過OV6620采集進來的;可編程器件CPLD采用Altera公司的EPM7128S,用Verilog硬件編程語言在QuartusII下編寫程序;作為系統的數據緩沖,SRAM選用的是IS61LV5128,其隨機訪問的特性為圖像處理程序提供了便利;而LPC2214在PLL(鎖相環)的支持下最高可以運行在60 MHz的頻率下,為圖像的快速處理提供了硬件支持。

OV6620集成在一個板卡上,有獨立的17 MHz晶振。輸出3個圖像同步的時序信號:像素時鐘PCLK、幀同步VSYNC和行同步HREF。同時,還可以通過8位或16位的數據總線輸出RGB或YCrCb格式的圖像數據。

在硬件設計上,有2個問題需要解決:

① 圖像采集的嚴格時序同步;

② 雙CPU共享SRAM的總線仲裁。

解決第一個問題的關鍵在于如何實時、準確地讀取OV6620的時序輸出信號,據此將圖像數據寫入SRAM中。這里采用的解決方案是用CPLD來實現時序信號的識別以及圖像數據的寫入。CPLD在硬件上可以識別信號的邊沿,速度更快,通過Verilog語言編寫Mealy狀態機來實現圖像數據的SRAM寫入,更加穩定。

對于雙CPU共享SRAM,可以通過合理的連接方式來解決。考慮到CPLD的可編程性,將OV6620的數據總線,LPC2214的地址、數據總線以及SRAM的總線都連接到CPLD上。通過編程來控制總線之間的連接,只要在軟件上保證總線的互斥性,即在同一時刻有且僅有一個控制器(CPLD或者LPC2214)來操作SRAM的總線,就可以有效地避免總線沖突。這樣,硬件上的仲裁就可以通過軟件來保證,該過程可以通過在CPLD中編寫多路數據選擇器來實現。

各器件之間的連接關系如圖1所示。

圖1 系統結構框圖

評論