一種基于FPGA的高速誤碼測試儀的設計

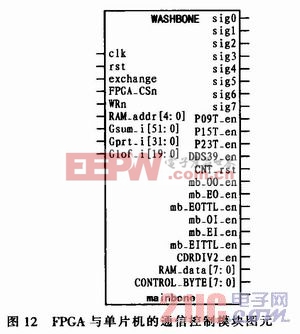

1.6 FPGA與單片機通信的控制模塊

FPGA與單片機的通信控制模塊(washbone moudle)實現的功能有:1)控制FPGA發送數據(總碼數、誤碼數、誤碼塊數)到數據線上;2)控制FPGA接收單片機發送到數據線上的控制數據。FPGA與單片機的通信控制模塊將FPGA接收到的控制信息產生控制其他模塊的信號,這些控制信號包括SY87739L頻率合成的使能信號,SY87700V控制模塊的使能信號,計數器復位信號,偽隨機碼的級數、速率、發送接收接口的控制信號等。由源程序綜合出的圖元如圖12所示。本文引用地址:http://www.104case.com/article/191002.htm

當SY87700V提取的數據頻率為30.72 MHz時,SY87700V的參考頻率為3.84 MHz。圖13為FPGA與單片機的通信控制模塊的功能仿真結果。該仿真是對washbone模塊中控制FPGA接收單片機控制數據這一功能的仿真。在測試文件中RAM_data FPGA與單片機的通信數據信號賦值為0001010(控制該模塊產生P09T_en、mb_OO_en、mb_OI_en為高電平的信號);exchange賦值高電平,既FPGA將數據(總碼數,誤碼數,誤碼塊數)存入FPGA的內部存儲單元;FPGA GSn=0.WRn=1既FPGA讀取數據線上的數據,并存入內部寄存器memory中。在該模塊的輸出管腳中:P09T _en、mb_OO_en、mb_OI_en輸出為高電平,既控制偽隨機發送模塊合成9級m序列,發送、接收的端口類型都為光接口類型。從下列仿真圖中可以判斷該模塊可以實現要求的邏輯功能。

2 各模塊綜合結果

2.1 綜合報告

綜合優化(SyntIlesize)是指將HDL語言、原理圖等設計輸入翻譯成由與、或、非門,RAM,寄存器等基本邏輯單元組成的邏輯連接(網表),并根據目標與要求(約束條件)優化所生成的邏輯連接,輸出edf和edn等文件,供FPGA廠家的布局布線器進行實現。

在本設計中使用綜合工具Synplify Pro8.1進行綜合,該綜合工具綜合出的結果占用面積小、工作頻率高,綜合速度快。目前FPGA技術中最流行的高效綜合工具之一。FPGA中各模塊通過綜合工具Synplify Pro8.1綜合。在綜合前,在時序約束文件中將分頻系數為100分頻的分頻器時鐘約束為10.0MHz;接收模塊中合成m序列的同步時鐘CDR00TKP約束為125.0 MHz;CDRK輸入的是7.68 MHz的晶體振蕩器產生的時鐘,FPGA根據合成m序列的速率,判斷CDRK是否進行二分頻,FPGA將處理后的CDRK作為提取時鐘芯片的參考時鐘。該時鐘約束為7.68 MHz;

DDS39REFCLK是時鐘合成模塊的參考時鐘,該時鐘約束為30MHz:DDS39TKP輸入的是時鐘合成芯片SY87739L的合成時鐘,該時鐘用于發送模塊產生m序列的同步時鐘,DDS39TKP約束為95 MHz。

從綜合報告中可以看出綜合后各個時鐘的綜合結果都超出了約束的頻率,滿足時序的要求。此外還可以從報告中得到FPGA中的資源利用情況:使用59個I/O原語資源,使用了0個I/O寄存器.使用了775個非I/O寄存器占FPGA總資源的50%,使用的總邏輯資源為1 253個查找表,占總資源的81%。

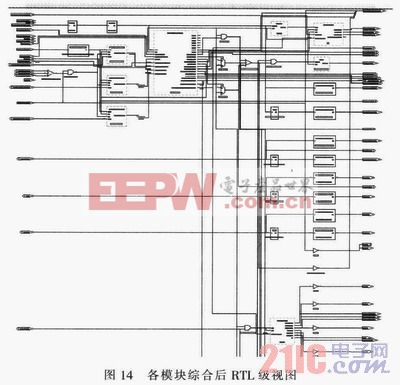

2.2 RTL(寄存器級)視圖

RTL視圖是由與、或、非門,RAM,寄存器等基本邏輯單元組成邏輯連接圖,從中可以形象的得到FPGA中各模塊的連接情況,并能判斷硬件描述語言編寫出來的系統在邏輯上是否正確。圖14是由Synplify綜合出的RTL視圖。

分析上圖中各模塊的連接情況可以判斷出由Verilog編寫出的程序在各模塊的邏輯連接設計上是正確的,可將綜合后的edf文件輸送給Xinlinx布局布線器實現。

3 結束語

本文研究的內容是一種用于高速通信系統中的誤碼測試儀。該高速信號誤碼測試儀是基于FPGA(現場可編程門陣列)為核心設計而成,適用于斷線誤碼檢測。誤碼測試儀在發送端發送m序列作為測試數據,其測試速率最高可達到155Mbps。對于高速數字電路迅速發展的今天,此誤碼測試儀的測試速率還可進一步提高,但是一旦提高了誤碼測試儀的工作速率,就無法回避高速數字電路中信號完整性,電磁干擾等高速數字電路設計中要注意的問題。由于使用FPGA實現誤碼測試儀的核心功能,該系統具有可以升級的特點。

設計中軟件部分采用的是Verilog硬件語言編寫程序,軟件開發環境使用的是Xflinx公司的EDA集成開發工具ISE8.1,仿真工具ModelSim SE 6.1b,綜合工具SynplifyPro8.1等幾款軟件。硬件實現采用的是Xilinx的SPARTANHE系列中的XC2S50E平臺級FPGA為核心功能芯片。在FP GA中實現誤碼測試儀的發送部分、接收部分及誤碼量統計模塊的設計。輔以時鐘合成芯片Micrel SY87739L、時鐘提取芯片Micrel SY87700V及單片機(C8051F010)的控制,整個系統的體積較小,成本也較低。

評論