基于FPGA的PEX8311的LBS控制器的實現

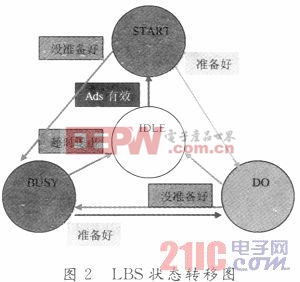

2.4 LBS狀態機設計

LBS共設計有4個狀態:IDLE,START,DO,BUSY。其狀態轉移圖如圖2所示。本文引用地址:http://www.104case.com/article/190888.htm

IDLE:空閑狀態。

START:當ADS地址選通有效時進入此狀態,進行地址空間判斷。

DO:當地址空間有效,并且傳輸條件滿足時進入傳輸狀態,每個時鐘判斷條件,當條件滿足時繼續該狀態,當條件不滿足時,進入BUSY等待狀態,傳輸結束(BLAST有效)進入IDLE狀態。

BUSY:當數據沒準備好時,在BUSY狀態等待,當數據準備好后進入DO狀態,當超時后進入IDLE狀態,實時退出。

2.5 LBS狀態機工作流程

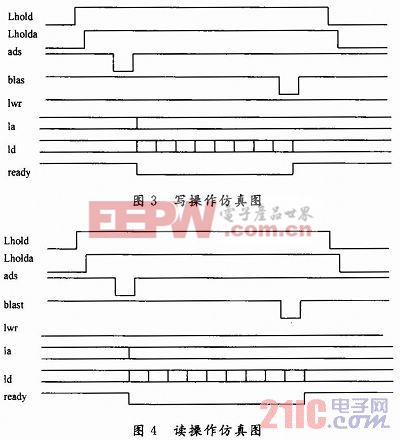

FPGA作為LBS的邏輯控制器,負責協調好與DDR_FIFO數據和PEX8311之間的時序關系。系統接收數據時,首先由驅動程序向PEX8311發送復位信號,通過LRESET復位LBS本地端的FPGA,清空FPGA內部DDR_FIFO內部數據,并將HF和FF標志置為無效,然后等待數據的輸入。FPGA讀入DDR數據后,首先將DDR數據寫入DDR_FIFO中,當DDR_FIFO中的數據達到半滿狀態時,HF標志位有效,通過FPGA向PEX8311發出DMA中斷請求。PC機響應中斷后,設置DMA傳輸模式,傳輸字節數及地址信號等。PEX8311通過LHOLD申請控制本地總線,此時FPGA發出的LHOLDA響應信號后獲得本地總線的控制權,并立即進入連續字節突發模式的Block DMA周期即由IDLE狀態到START狀態。FPGA在收到有效的LW/R讀信號和ADS地址選通信號后,進入DO狀態,同時發出Ready本地準備好應答信號,使能DDR_FIFO的讀允許REN和輸出允許OE。在傳輸最后一個數據時,PEX8311發出BLAST信號,FPGA配置DDR_FIFO讀使能和輸出使能無效,并取消Ready從而結束DMA周期。PC系統發送數據時,FPGA將計算機通過PCIe傳過來的LBS數據寫入PC_FIFO中,再輸出寫入到DDR中。

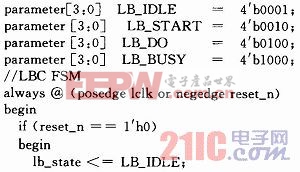

2.6 LBS狀態機核心編碼設計

按照上述4個狀態進行Verilog設計,經過仿真和上板調試,效果很好,下面是狀態機設計程序,仿真時序圖如圖3,圖4所示。

評論