基于CPLD的簡易數字頻率計的設計

摘要:CPLD器件的出現給現代電子設計帶來了極大的方便和靈活性,使復雜的數字電子系統設計變為芯片級設計,同時還可以很方便地對設計進行在線修改。首先介紹了頻率計的測頻原理,然后利用CPLD芯片進行測頻計數,從而實現了簡易數字頻率計的設計。此頻率計的設計采用基于VHDL的“Top-Down”(自上而下)的設計方法,從系統總體要求出發,自上而下地逐步將設計內容細化,最后完成系統硬件的整體設計。所設計的電路在GW48系列SoPC/EDA實驗箱上通過硬件仿真,下載到目標器件上運行,能夠滿足實際測量頻率的要求。

關鍵詞:CPLD;VHDL;頻率計;設計

0 引言

目前已經有不少文獻分別從不同的角度對此問題進行了討論和研究。有基于FPGA實現的,FPGA的保密性差,它的分段式布線結構決定了其延遲的不可預測性,它的編程信息需存放在外部存儲器上,使用方法復雜;也有用標準邏輯器件實現的,用標準邏輯器件使系統布線復雜、體積功耗大、可靠性差、設計周期長,交流和修改不方便。該頻率計采用先進的EDA技術及自上而下的設計,使用CPLD芯片,CPLD具有連續連接結構,易于預測延時,使電路仿真更加準確,且編程方便、速度快、集成度高、價格低,從而使系統研制周期大大縮短,產品的性能價格比提高。本頻率計采用流行的VHDL語言編程,并在設計平臺實現了全部編程設計。該數字頻率計的設計及實現具有良好的應用價值和推

廣前景。下面對該頻率計的軟硬件設計進行詳細論述。

1 測頻原理

1.1 頻率的定義

頻率定義為在單位時間內,記錄被測信號的變化周期數(或脈沖個數)。若記錄被測信號的的變化周期數(或脈沖個數)為Nx,則被測頻率Fx的數值為Nx,單位為:Hz。

1.2 基本性能指標

測頻范圍為:1 Hz~1 MHz;

測頻精度:相對誤差為1 Hz。

1.3 頻率計的功能分析

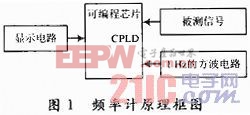

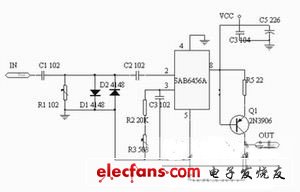

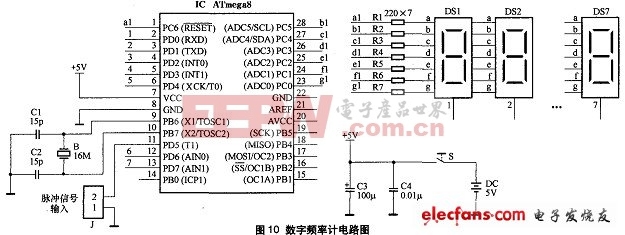

由于數字頻率計是一個需對數字信號進行測量和顯示的系統,由一片CPLD完成各種測試功能(對被測信號進行計數等),最后將測量結果送數碼管顯示輸出,因此測頻需要設置控制電路、計數電路、鎖存電路、譯碼電路,將這些電路設計好的各部分連接起來成為一個整體的電路寫人CPLD芯片中,外圍電路由顯示電路、產生1 Hz的方波電路組成。

控制電路是對計數電路、鎖存電路和譯碼電路進行時序的控制。其控制要求為:先使計數電路在1 s內進行計數,接著在下一個1 s內鎖存計數的結果,最后將鎖存的數據進行譯碼和顯示。在第一個測量顯示周期結束后,控制電路將再次發出控制信號,先對功能電路清零,然后使系統開始第二個測量周期的工作。

計數電路是對被測信號的頻率進行計數的主功能電路。根據頻率的定義和測頻的基本原理,必須由一個脈寬為1 s的對被測信號脈沖計數的允許信號,其測量結果為被測信號在1 s內的脈沖個數,即被測信號的頻率。由于被測信號的頻率測頻范圍為1 Hz~1 MHz,因此用計數電路測量時,使用6個輸出為4位的二進制數計數器。此計數器從個位開始到高位分別進行計數,使低位計數器的進位與高位計數器的被測信號輸入端相連,從計數器電路的結構可知,該電路輸出信號是由從低位到高位的多組4位二進制表示的十進制數組成的,用來分別表示被測信號的個、十、百、千等位的數值。

鎖存電路的主要功能是對計數器計數輸出的數據進行鎖定保存。即使在前級計數電路的計數器清零以后,鎖存器依然有保存的數據存在,不會造成數據的丟失。鎖存電路中的鎖存器是對單個十進制計數器數據進行保存,因此鎖存器的個數與前一級計數電路的十進制計數器的個數相同。

譯碼電路的功能是將鎖存器保存并將輸出的4位二進制代碼表示的十進制數進行譯碼轉換,將其轉換為能直接驅動數碼管顯示的十進制數字字符的輸出信號。

顯示電路由共陰數碼管電路構成。由于被測信號的頻率測頻范圍為1 Hz~1 MHz,因此需要6個數碼管對其進行顯示。

2 頻率計各模塊設計

2.1 頻率計原理框圖

此頻率計的流程為:被測信號fin輸入到CPLD芯片,在控制信號為1 Hz時,在CPLD芯片里完成對被測信號的測頻、計數、鎖存、譯碼,輸出信號接數碼管顯示,如圖1所示。

評論