一種多通道時鐘分頻和觸發延遲電路的設計

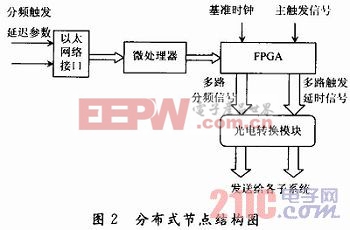

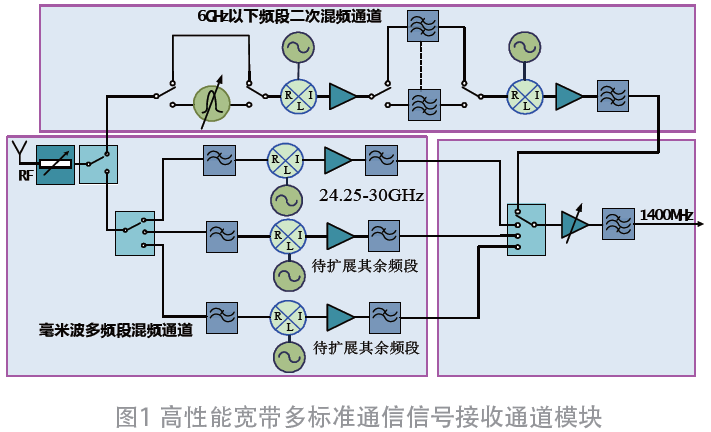

分布式節點是該中央定時觸發系統的核心,而時鐘分頻和觸發延遲也是分布式節點最重要的任務。分布式節點主要由微處理器和FPGA組成,外圍由以太網絡端口,光電轉化模塊等等組成。微處理器接收核心模塊發送的分頻系數和延遲參數,FPGA主要根據微處理器傳輸來的參數對輸入的基準時鐘進行相應的分頻,并對核心模塊發送的主觸發信號進行延遲輸出。時鐘同步系統分布式節點結構如圖2所示。本文引用地址:http://www.104case.com/article/190787.htm

2 時鐘分頻設計

對基準時鐘的整數分頻主要分為等占空比偶數分頻和等占空比奇數分頻,它們的分頻原理也是不同的,必須要分別對待。對于單通道偶數分頻,設計比較簡單,之前已經有很多這方面的研究,在此不再贅述。在本設計中,由于EAST定時觸發系統需要多路分頻信號,可以在程序設計的時候采用VHDL里面的類屬參量和元件例化語句,類屬參量Generic是一種端口界面常數,常以一種說明的形式放在實體或塊結構體前的說明部分。類屬參數映射的綜合處理較簡單,所有的參數配置都通過Generic map來傳遞,子模塊內部只需要根據上層模塊指定的參數進行綜合即可。整數時鐘分頻電路需要在一個程序中可以同時對基準時鐘進行奇數和偶數分頻,所以在頂層文件中需要聲明元件的語句格式如下:

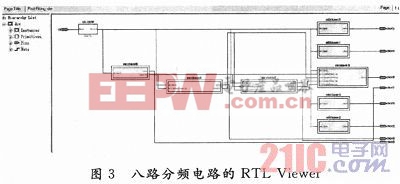

時鐘分頻設計的RTL Viewer,即在FPGA中所設計的電路原理圖如圖3所示,所有的計數分頻模塊都采用同樣的基準時鐘,以保證每路時序信號能夠完全的同步。

評論