一種多通道時鐘分頻和觸發延遲電路的設計

摘要:在EAST分布式中央定時同步系統中,時鐘分頻和觸發延遲電路是分布式節點的核心。為了完成對基準時鐘信號進行多路任意整數倍的等占空比的分頻,并對輸入的觸發脈沖進行多路任意時間的延遲輸出,本設計中采用VHDL語言進行編程,實現了多路時鐘分頻信號的輸出和多路延遲輸出,特別是提高了奇數分頻和觸發延遲的時間精度,最后在QuartusⅡ9.0軟件上時設計的波形進行分析,驗證了該設計的可行性。

關鍵詞:EAST;時鐘分頻;觸發延時;FPGA

0 引言

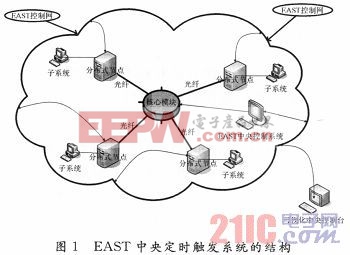

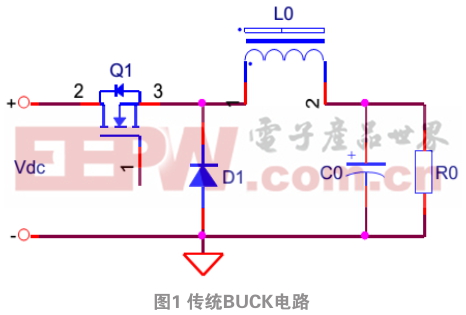

EAST(先進實驗超導托卡馬克)是我國自行設計研制的國際首個全超導托卡馬克裝置。中央定時同步系統是EAST托卡馬克裝置的重要組成部分。EAST中央定時與同步系統為分布廣泛的數據采集系統和其它子系統提供精確的方波時鐘信號,以及精確的同步觸發信號,控制各子系統按照預設的時序流程工作。該系統主要由EAST可視化中央控制臺,時序信號光纖網,核心模塊,若干個分布式節點以及外圍隔離驅動設備組成,見圖1。核心模塊負責向各分布式節點發送同步的基準系統時鐘和系統觸發信號。分布式節點根據設置對核心模塊發送的基準時鐘信號進行分頻,得到所需要頻率的時鐘發送到子系統。通過設置的觸發延遲模件參數可以得到子系統所需要的觸發時刻。

目前,進行分頻電路設計主要采用定時器來實現,8254計數器所支持的最高時鐘頻率有限(最高為10 MHz)以及誤差較大也不是理想的實現方案。可編程邏輯器件FPGA是當今最熱門的邏輯開發器件之一,它在工作最高頻率、集成度、時序控制能力上具有無與倫比的優勢。因此選用FPGA芯片來實現時鐘分頻和觸發延遲電路是當前的主流。在使用FPGA做時鐘分頻設計時,文獻設計計數器的時候用VHDL做了分頻器的設計,但是只討論了偶數的分頻;文獻在運動控制系統中使用Verilog描述語言在FPGA環境下對通用整數分頻器進行了設計,但在通用任意整數分頻器中分頻系數的設置稍顯復雜,不利于分布式中央定時系統,并且主要討論的都是單路輸出;文獻在FPGA上實現了奇數和偶數的通用分頻器,將半整數,奇數,偶數放在一個模N計數器里進行預置,這樣分頻系數的設定比較方便,但輸出奇數分頻時鐘信號時的誤差過大,達不到分布式定時同步系統的精度。而對觸發延遲輸出方面,之前這方面的研究主要采用的是模擬電路實現的方法,不易進行遠程控制和更改。

本文首先介紹中央定時同步系統的基本組成結構,隨后具體給出了時鐘分頻和觸發延遲電路的邏輯設計。利用FPGA芯片來實現對輸入基準時鐘信號進行多通道任意整數倍的等占空比分頻輸出,同時對觸發脈沖進行任意時刻延遲的多路輸出。本設計主要采用VHDL語言來設計,利用QuartusⅡ9.0對設計進行了仿真分析,結果表明該設計滿足分布式定時觸發系統的分頻延遲功能。

1 系統組成

EAST定時與同步系統主要由一個核心模塊和多個分布式節點構成,核心模塊給分布式節點提供一道基準時鐘信號和一道基準觸發信號,各分布式節點負責對基準時鐘和觸發進行分頻和延時處理,為子系統系統提供它所需要的時鐘和觸發。總體系統結構如圖1所示。

評論