Altera MAX10: 時(shí)鐘分頻

時(shí)鐘分頻

在之前的實(shí)驗(yàn)中我們已經(jīng)熟悉了小腳丫的各種外設(shè),掌握了verilog的組合邏輯設(shè)計(jì),接下來(lái)我們將學(xué)習(xí)時(shí)序邏輯的設(shè)計(jì)。

====硬件說(shuō)明====

時(shí)鐘信號(hào)的處理是FPGA的特色之一,因此分頻器也是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一。一般在FPGA中都有集成的鎖相環(huán)可以實(shí)現(xiàn)各種時(shí)鐘的分頻和倍頻設(shè)計(jì),但是通過(guò)語(yǔ)言設(shè)計(jì)進(jìn)行時(shí)鐘分頻是最基本的訓(xùn)練,在對(duì)時(shí)鐘要求不高的設(shè)計(jì)時(shí)也能節(jié)省鎖相環(huán)資源。在本實(shí)驗(yàn)中我們將實(shí)現(xiàn)任意整數(shù)的分頻器,分頻的時(shí)鐘保持50%占空比。

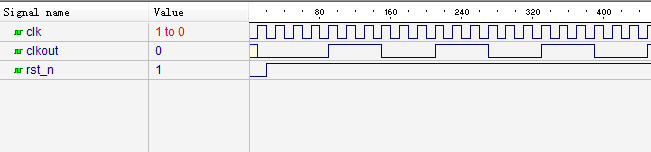

1,偶數(shù)分頻:偶數(shù)倍分頻相對(duì)簡(jiǎn)單,比較容易理解。通過(guò)計(jì)數(shù)器計(jì)數(shù)是完全可以實(shí)現(xiàn)的。如進(jìn)行N倍偶數(shù)分頻,那么通過(guò)時(shí)鐘觸發(fā)計(jì)數(shù)器計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),以此循環(huán)下去。

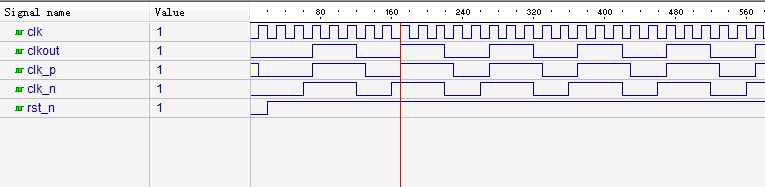

2,奇數(shù)分頻: 如果要實(shí)現(xiàn)占空比為50%的奇數(shù)倍分頻,不能同偶數(shù)分頻一樣計(jì)數(shù)器記到一半的時(shí)候輸出時(shí)鐘翻轉(zhuǎn),那樣得不到占空比50%的時(shí)鐘。以待分頻時(shí)鐘CLK為例,如果以偶數(shù)分頻的方法來(lái)做奇數(shù)分頻,在CLK上升沿觸發(fā),將得到不是50%占空比的一個(gè)時(shí)鐘信號(hào)(正周期比負(fù)周期多一個(gè)時(shí)鐘或者少一個(gè)時(shí)鐘);但是如果在CLK下降沿也觸發(fā),又得到另外一個(gè)不是50%占空比的時(shí)鐘信號(hào),這兩個(gè)時(shí)鐘相位正好相差半個(gè)CLK時(shí)鐘周期。通過(guò)這兩個(gè)時(shí)鐘信號(hào)進(jìn)行邏輯運(yùn)算我們可以巧妙的得到50%占空比的時(shí)鐘。

總結(jié)如下:對(duì)于實(shí)現(xiàn)占空比為50%的N倍奇數(shù)分頻,首先進(jìn)行上升沿觸發(fā)進(jìn)行模N計(jì)數(shù),計(jì)數(shù)選定到某一個(gè)值進(jìn)行輸出時(shí)鐘翻轉(zhuǎn),然后經(jīng)過(guò)(N-1)/2再次進(jìn)行翻轉(zhuǎn)得到一個(gè)占空比非50%奇數(shù)n分頻時(shí)鐘。再者同時(shí)進(jìn)行下降沿觸發(fā)的模N計(jì)數(shù),到和上升沿觸發(fā)輸出時(shí)鐘翻轉(zhuǎn)選定值相同值時(shí),進(jìn)行輸出時(shí)鐘時(shí)鐘翻轉(zhuǎn),同樣經(jīng)過(guò)(N-1)/2時(shí),輸出時(shí)鐘再次翻轉(zhuǎn)生成占空比非50%的奇數(shù)n分頻時(shí)鐘。兩個(gè)占空比非50%的n分頻時(shí)鐘進(jìn)行邏輯運(yùn)算(正周期多的相與,負(fù)周期多的相或),得到占空比為50%的奇數(shù)n分頻時(shí)鐘。

====Verilog代碼====

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : divide.v// Module name : divide // Author : STEP // Description : clock divider// Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2017/03/02 |Initial ver // -------------------------------------------------------------------- // Module Function:任意整數(shù)時(shí)鐘分頻 module divide ( clk,rst_n,clkout); input clk,rst_n; //輸入信號(hào),其中clk連接到FPGA的C1腳,頻率為12MHz output clkout; //輸出信號(hào),可以連接到LED觀察分頻的時(shí)鐘 //parameter是verilog里常數(shù)語(yǔ)句 parameter WIDTH = 3; //計(jì)數(shù)器的位數(shù),計(jì)數(shù)的最大值為 2**WIDTH-1 parameter N = 5; //分頻系數(shù),請(qǐng)確保 N < 2**WIDTH-1,否則計(jì)數(shù)會(huì)溢出 reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p為上升沿觸發(fā)時(shí)的計(jì)數(shù)器,cnt_n為下降沿觸發(fā)時(shí)的計(jì)數(shù)器 reg clk_p,clk_n; //clk_p為上升沿觸發(fā)時(shí)分頻時(shí)鐘,clk_n為下降沿觸發(fā)時(shí)分頻時(shí)鐘 //上升沿觸發(fā)時(shí)計(jì)數(shù)器的控制 always @ (posedge clk or negedge rst_n ) //posedge和negedge是verilog表示信號(hào)上升沿和下降沿 //當(dāng)clk上升沿來(lái)臨或者rst_n變低的時(shí)候執(zhí)行一次always里的語(yǔ)句 begin if(!rst_n) cnt_p<=0; else if (cnt_p==(N-1)) cnt_p<=0; else cnt_p<=cnt_p+1; //計(jì)數(shù)器一直計(jì)數(shù),當(dāng)計(jì)數(shù)到N-1的時(shí)候清零,這是一個(gè)模N的計(jì)數(shù)器 end //上升沿觸發(fā)的分頻時(shí)鐘輸出,如果N為奇數(shù)得到的時(shí)鐘占空比不是50%;如果N為偶數(shù)得到的時(shí)鐘占空比為50% always @ (posedge clk or negedge rst_n) begin if(!rst_n) clk_p<=0; else if (cnt_p<(N>>1)) //N>>1表示右移一位,相當(dāng)于除以2去掉余數(shù) clk_p<=0; else clk_p<=1; //得到的分頻時(shí)鐘正周期比負(fù)周期多一個(gè)clk時(shí)鐘 end //下降沿觸發(fā)時(shí)計(jì)數(shù)器的控制 always @ (negedge clk or negedge rst_n) begin if(!rst_n) cnt_n<=0; else if (cnt_n==(N-1)) cnt_n<=0; else cnt_n<=cnt_n+1; end //下降沿觸發(fā)的分頻時(shí)鐘輸出,和clk_p相差半個(gè)時(shí)鐘 always @ (negedge clk) begin if(!rst_n) clk_n<=0; else if (cnt_n<(N>>1)) clk_n<=0; else clk_n<=1; //得到的分頻時(shí)鐘正周期比負(fù)周期多一個(gè)clk時(shí)鐘 end assign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //條件判斷表達(dá)式 //當(dāng)N=1時(shí),直接輸出clk //當(dāng)N為偶數(shù)也就是N的最低位為0,N(0)=0,輸出clk_p //當(dāng)N為奇數(shù)也就是N最低位為1,N(0)=1,輸出clk_p&clk_n。正周期多所以是相與 endmodule

測(cè)試文件,進(jìn)行功能仿真時(shí)需要編寫testbench測(cè)試文件。verilog里的testbench文件和源文件一樣也是.v文件,仿真能讓我們更直觀的觀察信號(hào)波形,可以先閱讀Diamond的使用了解如何使用Diamond中集成的仿真工具。

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : divide_tb.v // Module name : divide_tb // Author : STEP // Description : clock divider // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2017/03/02 |Initial ver // -------------------------------------------------------------------- // Module Function:divide.v時(shí)鐘分頻器的測(cè)試文件 `timescale 1ns/100ps //仿真時(shí)間單位/時(shí)間精度,時(shí)間單位要大于或者等于時(shí)間精度 module divide_tb(); //測(cè)試文件也是一個(gè)module,因?yàn)橛糜诜抡嫠詿o(wú)需輸入輸出信號(hào) reg clk,rst_n; //需要產(chǎn)生的激勵(lì)信號(hào)定義,激勵(lì)信號(hào)需要過(guò)程塊產(chǎn)生所以定義為reg型變量 wire clkout; //需要觀察的輸出信號(hào)定義,定義為wire型變量 //初始化過(guò)程塊 initial begin clk = 0; rst_n = 0; #25 //#表示延時(shí)25個(gè)時(shí)間單位 rst_n = 1; //產(chǎn)生了一個(gè)初始25ns低電平,然后變高電平的復(fù)位信號(hào) end always #10 clk = ~clk; //每隔10ns翻轉(zhuǎn)一次clk信號(hào),也就是產(chǎn)生一個(gè)時(shí)鐘周期20ns的clk,頻率為50MHz //module調(diào)用例化格式 divide #(.WIDTH(4),.N(11)) u1 ( //#后面的()中為參數(shù)傳遞,如果不傳遞參數(shù)就是所調(diào)用模塊中的參數(shù)默認(rèn)值 //divide表示所要例化的module名稱,u1是我們定義的例化名稱,必須以字母開(kāi)頭 .clk (clk), //輸入輸出信號(hào)連接。 .clk表示module本身定義的信號(hào)名稱;(clk)表示我們?cè)谶@里定義的激勵(lì)信號(hào) .rst_n (rst_n), //在testbench里定義的信號(hào)名稱可以與所要調(diào)用module的端口信號(hào)名稱不同 .clkout (clkout) ); endmodule

====引腳分配====

小腳丫上的系統(tǒng)時(shí)鐘連接到FPGA的C1腳,時(shí)鐘為12MHz。你可以通過(guò)仿真波形觀察分頻時(shí)鐘(注意仿真的時(shí)間是有限的,所以分頻時(shí)鐘頻率需要較高)。如果我們想通過(guò)眼睛觀察LED的閃爍,那么需要設(shè)置參數(shù)N和WIDTH得到一個(gè)頻率較低的時(shí)鐘(例如N=12000000,WIDTH=24,分頻時(shí)鐘周期為1秒)。

| 信號(hào) | 引腳 |

|---|---|

| clk | J5 |

| rst_n | J9 |

| clkout | N15 |

修改程序中的分頻系數(shù)和計(jì)數(shù)器位數(shù)就能夠調(diào)整LED閃爍速度(注意計(jì)數(shù)的最大值一定要保證超過(guò)分頻系數(shù)N)。

====小結(jié)====

在本實(shí)驗(yàn)學(xué)習(xí)了如何進(jìn)行任意整數(shù)的分頻設(shè)計(jì),我們產(chǎn)生各種時(shí)鐘,通過(guò)修改程序還能實(shí)驗(yàn)調(diào)整輸出時(shí)鐘的頻率、相位以及占空比,非常靈活。同時(shí)學(xué)習(xí)了如何編寫testbench文件,了解verilog中如何例化module,在后面的學(xué)習(xí)中將會(huì)經(jīng)常用到。在下個(gè)實(shí)驗(yàn)我們將進(jìn)一步了解時(shí)序邏輯,如何利用時(shí)鐘來(lái)進(jìn)一步設(shè)計(jì),請(qǐng)看最常見(jiàn)的LED流水燈。

評(píng)論