基于FPGA的程控濾波器的設計

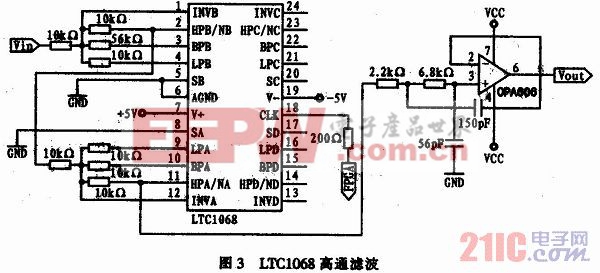

LTC1068的時鐘頻率與通帶之比為200:1,由于LTC1068內部對時鐘信號CLK二倍頻,所以當截止頻率最小為1 kHz時,內部時鐘頻率其實為400kHz,故在LTC1068后面再加一個截止頻率為450kHz的低通濾波器以濾除分頻帶來的噪聲及高次諧波。

3.3 低通濾波模塊

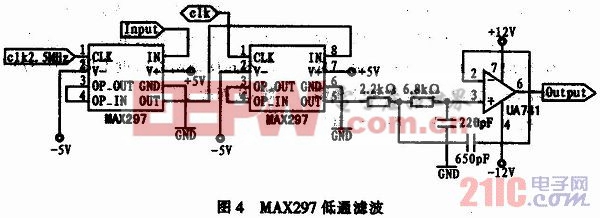

用MAX297實現低通濾波器。開關電容濾波器MAX297可以設置為8階低通橢圓濾波器,阻帶衰減為-80dB,時鐘頻率與通帶頻率之比為50:1。通過改變CLK的頻率,即可滿足濾波器-3 dB截止頻率在1~20kHz范圍內可調,步進1 kHz的要求。

在使用MAX297時要注意的是,當信號頻率和采樣辨率同頻,開關電容組在電容上各次采到相同的幅度為信號幅值的信號,相當于輸入信號為直流的情況,使濾波器輸出一個直流電平。同理,當信號頻率為采樣頻率的整數倍時,也會出現相同的現象。為此,在其前面,要增加模擬低通濾波器,把采樣頻率及其以上的高頻信號有效地排除。故又用一級MAX297,截止頻率設置為50kHz。其中時鐘頻率設置為2.5 MHz。在其后面,也要增加低通濾波器,其截止頻率為150 kHz,以濾去信號的高頻分量,使波形更加平滑。具體電路如圖4所示。

評論