PCI總線從設(shè)備接口的CPLD實現(xiàn)

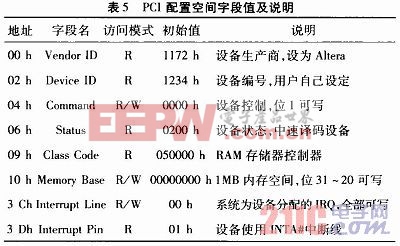

2.2 配置空間

配置空間是容量為256 Byte并具有特定記錄結(jié)構(gòu)或模型的地址空間,包括頭標(biāo)區(qū)和設(shè)備有關(guān)區(qū),前64 Byte是頭標(biāo)區(qū),用來唯一的識別設(shè)備,并使設(shè)備能以一般的方法控制,是PCI設(shè)備必須實現(xiàn)的。

本模塊實現(xiàn)了頭標(biāo)區(qū)所有的字段,可讀可寫字段中可寫的位由觸發(fā)器來實現(xiàn),其它位和只讀字段全部硬件連線接地或者接高。通過配置空間寄存器,配置軟件可以確定設(shè)備的存在、功能以及資源請求。配置空間主要字段的設(shè)置及含義說明如表5所示。本文引用地址:http://www.104case.com/article/190766.htm

2.3 譯碼

譯碼模塊包括命令譯碼、地址譯碼。在總線交易的地址期,譯碼模塊通過將AD信號線地址期的值與配置空間基址寄存器值相比較,確定訪問是否落在本設(shè)備的地址空間范圍內(nèi);或確定是否被選作配置訪問的目標(biāo)設(shè)備。同時對地址期C/BE信號線的值進(jìn)行命令譯碼,確定總線訪問的類型,本模塊支持配置讀、寫和內(nèi)存讀、寫4種PCI總線訪問方式。若譯碼后設(shè)備被選中,則發(fā)送HIT信號通知狀態(tài)機(jī)做進(jìn)一步處理。

2.4 數(shù)據(jù)通道

在總線交易的地址期,數(shù)據(jù)通道鎖存AD總線上的地址信號,并在IRDY#和TRDY#同時有效的時鐘上升沿,將地址自動增加一個雙字地址并提供給用戶接口。

在數(shù)據(jù)期,寫交易時將AD總線上的數(shù)據(jù)寫入配置空間或者用戶設(shè)備,在讀交易時數(shù)據(jù)通道負(fù)責(zé)將要讀出的配置數(shù)據(jù)或用戶設(shè)備數(shù)據(jù)鎖存送到AD總線上,并產(chǎn)生偶校驗值送給奇偶校驗?zāi)K。數(shù)據(jù)通道為PCI訪問配置空間和用戶設(shè)備提供了一個地址和數(shù)據(jù)接口。

2.5 奇偶校驗

奇偶校驗主要用來確定主設(shè)備是否成功的尋址到它希望的目標(biāo)設(shè)備,以及數(shù)據(jù)傳輸?shù)恼_與否,在總線交易中,任何設(shè)備驅(qū)動數(shù)據(jù)總線輸出數(shù)據(jù),就必須在相應(yīng)的地址或者數(shù)據(jù)的下一個時鐘周期驅(qū)動PAR線。設(shè)計中省去了奇偶校驗值的檢驗電路,只實現(xiàn)了必須的偶校驗值產(chǎn)生電路,計算出要輸出數(shù)據(jù)和CBE的偶校驗值后,在數(shù)據(jù)期的下一個總線時鐘周期送給主設(shè)備檢驗。

2.6 重試模塊

從設(shè)備接口如果承諾了一個數(shù)據(jù)交易,則必須在16個時鐘周期內(nèi)準(zhǔn)備好發(fā)送和接受數(shù)據(jù),否則超時重試。如果用戶設(shè)備被選作交易的從設(shè)備,但沒有準(zhǔn)備好,無法開始起始字節(jié)的數(shù)據(jù)交易,則狀態(tài)機(jī)一直處于等待狀態(tài),如果在規(guī)定的時間內(nèi)用戶設(shè)備仍沒有有效Ready信號,該模塊通知狀態(tài)機(jī)超時重試,然后斷開連接。

2.7 其他邏輯

該部分主要包括一個總線選擇器和一個三態(tài)總線驅(qū)動器。總線選擇器根據(jù)總線訪問的類型,選通配置空間讀數(shù)據(jù)或用戶設(shè)備數(shù)據(jù)送至數(shù)據(jù)通道;三態(tài)總線驅(qū)動器對輸出到用戶設(shè)備的數(shù)據(jù)進(jìn)行三態(tài)驅(qū)動。

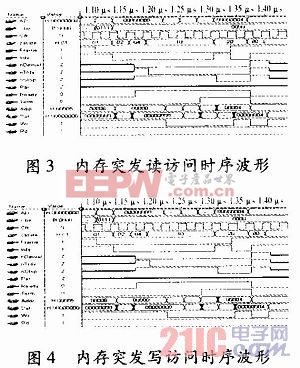

3 時序仿真

文中采用Verilog HDL語言設(shè)計實現(xiàn)了上述模塊,在Altera公司MAX+plusIl10.0軟件環(huán)境下,選用FLEX10K20RC208—3器件進(jìn)行綜合編譯,占用341個邏輯單元,最高工作頻率36 MHz,滿足PCI總線的時序要求。圖3是內(nèi)存突發(fā)讀訪問的時序仿真波形,突發(fā)傳輸4個數(shù)據(jù),在每個數(shù)據(jù)傳輸?shù)南聜€時鐘周期輸出奇偶校驗值,最后用戶設(shè)備提出終止傳輸請求,最后一個數(shù)據(jù)傳輸完成后交易結(jié)束。圖4是內(nèi)存突發(fā)寫訪問的時序仿真波形,突發(fā)傳輸4個數(shù)據(jù)后,主設(shè)備插入等待周期,同時用戶設(shè)備也有效Ready和Term請求終止傳輸,在第5個數(shù)據(jù)也是最后一個數(shù)據(jù)傳輸完成后,總線交易結(jié)束。這兩個時序圖屬于傳輸最后一個數(shù)據(jù)并斷開連接情形的兩種不同情況。仿真波形的分析表明,從設(shè)備接口模塊符合PCI規(guī)范的要求。

4 結(jié)束語

將一個FIFO模塊連接到PCI從設(shè)備接口的用戶總線組成測試平臺,由FIFO的狀態(tài)和控制信號提供同步的Ready和Term信號。這個測試平臺在MAX+plusII下編譯,并下載到PCI開發(fā)板上一片EPF10K20RC208-3芯片中,安裝驅(qū)動程序后,PCI開發(fā)板正確識別、工作穩(wěn)定、讀、寫數(shù)據(jù)準(zhǔn)確無誤;多組數(shù)據(jù)傳輸測試,測得數(shù)據(jù)突發(fā)傳輸率約可達(dá)到20 MB·s-1。

評論