基于FPGA的SDX總線與Wishbone總線接口設計

3 系統設計與實現

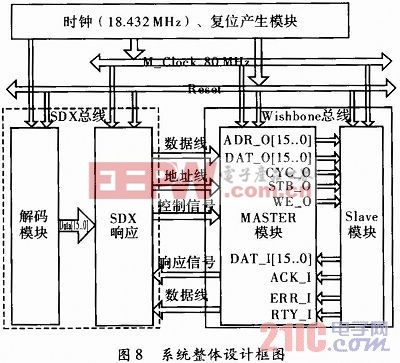

系統所有控制邏輯均在Altera的CycloneⅢ系列FPGA(EP3C40F)上實現。FPGA的信號線只有系統時鐘、串行輸入數據,由于SDX總線中傳輸數據為曼徹斯特碼型,因此需將曼徹斯特碼解碼為BCD碼同時將串行輸入數據轉化為并行數據,將轉化后標準的16位并行BCD碼輸入SDX模塊對SDX協議響應,將需要數據讀、寫的消息響應同時產生數據讀、寫以及地址信號并發起Wishbone總線操作,實現在Wishbone總線上高效的數據傳輸。Wishbone總線主要使用點對點的互聯方式,將Wishbone總線中Master模塊中的輸出信號直接連接到Slave模塊,其優點是多個數據可以并行處理,從而提高系統的整體數據處理能力。系統的整體設計框圖如圖8所示。本文引用地址:http://www.104case.com/article/190721.htm

4 仿真結果分析

為驗證設計系統的性能,使用Modelsim6.2仿真軟件對系統功能進行了仿真測試。

圖9為Wishbone總線寫操作,且為單字寫傳輸,在時鐘上升沿,Master將DAT_O、ADR_O信號放到數據、地址總線上,將CYC_O、STB_O、WE_O置高表示寫傳輸開始,在下一個時鐘沿到達之前,Slave檢測到Master發起的操作,將ACK_O、ERR_O、RTY_O之一置高并傳輸到Master中,若Master檢測到ACK_I為高時,在下一個時鐘的上升沿將CYC_O、STB_O置低表示操作完成,若ERR_I為高,則表示該操作錯誤,取消此操作,進行下一步操作,若RTY_I表示Slave總線忙,則重試。

圖10為Wishbone總線讀操作,且為單字讀傳輸,在時鐘上升沿,Master將ADR_O信號放到地址總線上,WE_O保持為低,同時將CYC_O、STB_O置高表示讀傳輸開始,在下一時鐘沿到達之前,Slave檢測到Master發起的操作,將ACK_O、ERR_O、RTY_O之一置高并傳輸到Master中,同時將適當的數據傳輸到Master的DAT_I中,若Master檢測到ACK_I為高時,在下一個時鐘的上升沿將CYC_O、STB_O置低表示該次讀操作完成,若ERR_I為高,則表示該操作錯誤,則取消此操作,進行下一操作,若RTY_I表示Slave總線忙,則重試。

5 結束語

討論了基于FPGA的SDX總線與Wishbone總線的接口轉換,并介紹了不同總線的接口標準與時序,通過在Modelsim下的仿真,Quartus中綜合,可下載到FPGA中進行調試,實現了系統的整體性能,從而保證了系統快速、高效的傳輸。

評論