一種基于FPGA的數(shù)字秒表設計方法

該模塊的源程序以及ModelSim仿真輸出結果如下:本文引用地址:http://www.104case.com/article/190686.htm

模10計數(shù)器的VHDL源程序與模6計數(shù)器類似,為節(jié)省篇幅,不再給出。

2.3 使能信號轉換模塊

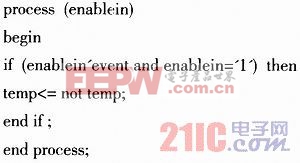

數(shù)字秒表輸入的開始和停止信號是單個脈沖信號,而計數(shù)器要持續(xù)計數(shù)所需的使能信號是持續(xù)的高電平,所以需要通過使能控制電路實現(xiàn)使能信號的轉換。該模塊的VHDL源程序以及ModelSim仿真輸出結果如下:

該模塊源程序:

2.4 譯碼顯示模塊

由上面的設計可知,計數(shù)器輸出為二進制碼,不能直接點亮數(shù)碼管,要想將計數(shù)結果通過數(shù)碼管顯示必須再設計一個七段譯碼電路,以便將計數(shù)結果輸出。通過分析可知該譯碼器是一個4輸入,7輸出元件,其真值表如表1所示:

評論