基于FPGA高速數據采集與傳輸的聲幅測井系統

3 系統軟件設計

設計的數據采集系統是基于高性能FPGA芯片實現的,FPGA承擔了絕大部分的控制和數據處理任務,是設計的核心內容,對FPGA進行模塊化設計,是大型系統設計的常用方法。本項目中將FPGA分成USB控制模塊、采樣控制模塊、觸發脈沖產生模塊和RAM等幾個主要功能模塊來設計。

FPGA模塊的原理如圖3所示。其工作原理為觸發脈沖產生模塊,根據設定的參數周期性輸出脈沖信號觸發采樣控制模塊對A/D進行采樣。采樣控制模塊在接收到USB控制模塊的啟動信號后,只要接收到觸發信號就開始采樣數據,并判斷采樣數據是否滿足要求,如果滿足要求則把數據存放于RAM中,且在采樣結束后觸發USB控制模塊上傳數據。本文引用地址:http://www.104case.com/article/190675.htm

通電后,先對USB芯片初始化,然后如果接收到采樣結束信號或上傳結束信號并且RAM在還剩余有數據的條件下把RAM數據上傳,若接收到下傳信號,則把計算機下傳的數據按要求分配到各端口。

3.1 采樣控制模塊

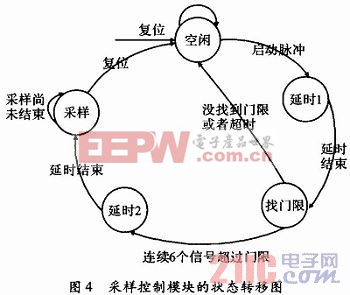

采樣控制模塊根據外部觸發信號,利用狀態機對A/D的采樣行為進行控制。共有5個狀態,每個狀態的動作在代碼中進行了詳細描述。

第1個狀態:空閑狀態(IDLE),表示程序無任何操作,在等待外部觸發信號的到來。

第2個狀態:延時1(第一個等待狀態,WAIT1),表示收到觸發信號后需要禁閉A/D一段預先設定的時間,這段時間不進行任何操作。

第3個狀態:找門限(門限判決狀態,THDET),在規定的時間段時間里判斷A/D采樣的信號中是否有連續6個采樣大于門限的值,如果有,等待一段時間后把采樣后的數據存入緩沖區以便上傳給上位機。否則繼續等待下一個觸發信號。

第4個狀態:延時2(第二個等待狀態,WAIT2),表示已經滿足采樣要求后再禁閉A/D一段預先設定的時間,這段時間不進行任何操作。然后啟動A/D進行采樣。

第5個狀態:采樣狀態(SAMPER),啟動A/D進行采樣,并存儲數據。

此處為米莉(Mealy)型狀態機,Mealy型狀態機的輸出不僅與現態有關,而且和輸入也有關。

該狀態機采取3段式描述方式:即使用3個always塊,第1個always塊采用同步時序描述狀態轉移;第2個always塊采用組合邏輯判斷狀態轉移條件,描述狀態轉移規律;第3個always塊描述狀態輸出。

狀態機的編碼使用獨熱碼(One-hot)編碼,獨熱碼編碼的最大優勢在于狀態比較時僅需要比較一個位,從而一定程度上簡化了比較邏輯,減少了毛刺產生的概率。

評論