基于FPGA高精度浮點運算器的FFT設計與仿真

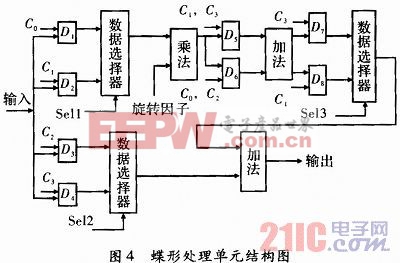

1.3.1 蝶形處理單元

蝶形處理單元是整個FFT的中心環節,采用復數表示,將實部與虛部分別存儲,利用基2的DIT-FFT算法實現運算。本文引用地址:http://www.104case.com/article/190672.htm

蝶形運算過程包括一個乘法運算![]() 和一個加/減法運算

和一個加/減法運算![]() 。數據的讀取由時鐘單元的信號來控制:當時鐘為c0時,讀取y;c1時,讀取Y;c2時,讀取x;c3時,讀取X。經蝶形運算后得到x’=x+(ycosφ+Ysinφ),X’=X+(Ycosφ-ysinφ),y’=x-(ycosφ+Ysinφ),Y’=X-(Ycosφ-ysinφ)然后將數據寫入同樣地址的RAM中,至此,2點的蝶形運算單元完成。在蝶形運算共需一個乘法器和兩個加法器。

。數據的讀取由時鐘單元的信號來控制:當時鐘為c0時,讀取y;c1時,讀取Y;c2時,讀取x;c3時,讀取X。經蝶形運算后得到x’=x+(ycosφ+Ysinφ),X’=X+(Ycosφ-ysinφ),y’=x-(ycosφ+Ysinφ),Y’=X-(Ycosφ-ysinφ)然后將數據寫入同樣地址的RAM中,至此,2點的蝶形運算單元完成。在蝶形運算共需一個乘法器和兩個加法器。

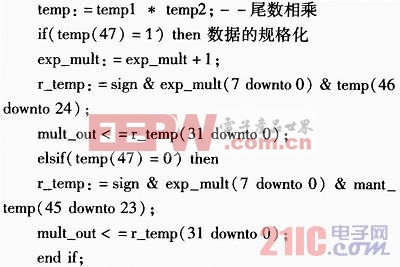

(1)浮點乘法器。乘法過程對浮點數的符號位、指數以及尾數分別進行計算,符號異或,指數相加再減127,尾數加入隱含的‘1’后再進行乘法運算,如果尾數相乘的結果有溢出則指數加1尾數取前23位,若無溢出,則取最高位后的23位。但若輸入的數據有一個是0,則輸出為0。

圖5的波形為兩浮點數的乘法運算,輸入以16進制表示,分別將不同類型的數據搭配進行測試,結果表示仿真正確。

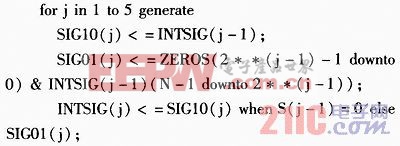

(2)浮點加法器。加法運算是將兩數指數比較,存儲較大的指數,將指數小的尾數移位,再進行加減操作,規格化后輸出。加法過程由多個模塊組合實現,包括比較模塊,右移模塊、加/減法模塊、前導零檢測模塊、左移模塊和結果整合輸出模塊。

比較模塊主要對指數操作,判斷指數的大小,較大的指數暫作結果的指數,較小指數的數做移位操作,其階差為移位量。以下程序采用for循環來實現移位,S(5 downto 0)存儲階差,最大值是32。

fpga相關文章:fpga是什么

評論