基于FPGA的UART、USB接口協議設計

一、PC終端概述

本文引用地址:http://www.104case.com/article/190660.htmPC終端,Personal Computer 智能終端,通俗的講,就是利用電腦GUI界面控制我們的外部硬件電路。

因此設計到了PC與外部硬件電路的通信接口。對于臺式電腦、個人筆記本,最常用的接口就是USB接口、串口、并口、PS2接口、網口。在我們電子設計中的PC終端軟件的通信,應用最多的就是串口、其次是USB接口、再就是網口。(對于現在大部分筆記本沒有了串口,我們可以用USB專串口線來代替。)這三種接口速度和性質不同,各有千秋:

(1)電子產品中,很多低速的數據采集,一些點陣系統的配置,GPRS模塊的調試等,都用串口來實現跟PC的通信。甚至一些單片機(宏晶STC)的配置都用串口實現通信。串口最高可以達到128000bps的速率,在低速場合下,完全能夠實現與PC的通信,來滿足我們各種要求,來實現對數據的實時處理。

(2)設計到高速的數據傳輸、視頻圖像傳輸等的,一般用USB接口來交換數據。比方說我們的硬盤、U盤、各種硬件下載器(USB BLUSTERO(∩_∩)O哈哈~)、以及實時圖像采集、視頻采集等,都是用USB接口來實現的。目前USB已經發展到了USB 3.0,但還是以USB 2.0為主,最高能夠達到480Mbps(60MB/s)高速,足夠的帶寬滿足我們對高速、海量數據的采集處理。

(3)最后就是網口的通信,一般網口用來上網傳輸數據,但是也可以用來硬件和PC之間的數據傳輸。一般網絡,千兆的能力,NetFPGA,用FPGA實現的通信協議,早已不是夢想。近年來流行的網絡攝像頭,就是通過網絡來傳輸(當然也有通過WiFi飛);現在超市、廣場的超大真彩點陣是數據傳輸,由于數據量之大,一般采用網絡傳輸,來達到顯示的實時性。

最后,我們的PC終端軟件,就是通過C++、MFC、C#等語言編寫軟件,對這些接口的驅動,來對數據的采集處理,從而達到用戶預期的要求。本章中主要講解FPGA硬件平臺的UART、USB通信接口的軟硬件設計,并且對Bingo的代碼設計稍作分析,希望對你有用。

二、UART通信接口設計

1、UART通信協議

UART:Universal Asynchronous Receiver/Transmitter,通用異步接收/發送裝置,所謂異步,就是說發送和接受不能同時進行,是單工的。對于UART的verilog設計,簡單的說就是需要“波特率發生器”與“數據傳輸時序”兩個模塊,如下:

(1)波特率

在UART通信協議中很重要的一個定義,就是“波特率”,即傳輸數據時的速率。波特率一般有以下這些:

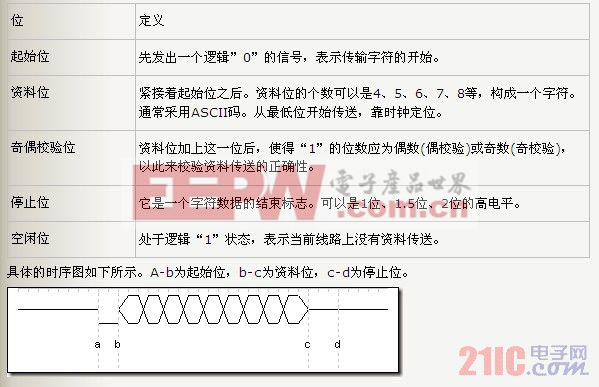

(2)數據傳輸時序

對于UART數據傳輸的協議,如下所示。其中奇偶校驗位與停止位不是必須的。而“起始位、資料位、停止位”則是必須的。一般資料位為8 bits。

2、UART硬件設計

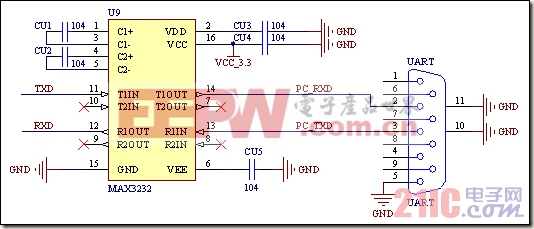

UART是計算機中串行通信端口的關鍵部分。在計算機中,UART相連于產生兼容RS232規范信號的電路。RS232標準定義邏輯“1”信號相對于地為-3到-15伏,而邏輯“0”相對于地為3到15伏。所以,當一個微控制器中的UART相連于PC時,它需要一個RS232驅動器來轉換電平。

如下圖所示,UART硬件電路灰常的簡單,只需要一塊電平轉換芯片即可。電平轉換芯片一般用Max3232、Max232,SP3232等,其中Maxim公司的電平轉換芯片比較常用。跟PC和處理器相連接的,只要相應的TXD、RXD兩根信號線即可。

3、UART Verilog設計

基于FPGA的UART設計,其實在單片機中沒有這么一說。單片機中早已有了UART的IP,我們只要調用函數即可,但FPGA中,純硬件設計電路上,我們想要使用串口來調試,那我們就必須了解徹底UART通信協議,必須自己動手寫UART的硬核。利用硬件描述語言,相當的方便。

UART驅動代碼的編寫,算是比較簡單的設計了。Bingo當年用VHDL編寫串口通信,后來學了Verilog,重新來過,最后修改串口,改善得到穩定的版本,經過多次測試,上萬數據傳輸未出現過錯誤,已應用于多個項目中,在此獻丑,希望對你有用。

以下是相關的下載信息:

(1)串口調試助手

http://www.chinaaet.com/lib/detail.aspx?id=86809

(2)uart_io_test工程

http://www.chinaaet.com/lib/detail.aspx?id=86812

(3)uart_fifo_design工程

http://www.chinaaet.com/lib/detail.aspx?id=86813

對于基于FPGA的Verilog設計UART通信接口的代碼分析,如下所示:

(1)波特率發生器

如果您看過前面章節,那您是否還記得“第九章 為所欲為——教你什么才是真正的任意分頻”?此處我們為了達到標準的頻率,最大極限的不想出現任何誤差,Bingo利用自己設計的“相位控制分頻原理”,來完成此模塊的設計。具體的分頻原理請看第九章,此處不再做累贅的闡述,謝謝。

關于本模塊的主要代碼,如下:

/*************************************************

* Module Name : clk_generator.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011/01/27

* Revision : v1.0

* Description :

**************************************************/

module clk_generator

(

input clk,

input rst_n,

output clk_bps,

output clk_smp

);

//------------------------------------------

/************clk_smp = 16*clk_bps************

Freq_Word1 = 32'd25770; Freq_Word1 = 32'd412317; //300 bps

Freq_Word1 = 32'd51540; Freq_Word2 = 32'd824634; //600 bps

Freq_Word1 = 32'd103079; Freq_Word2 = 32'd1649267; //1200 bps

Freq_Word1 = 32'd206158; Freq_Word2 = 32'd3298535; //2400 bps

Freq_Word1 = 32'd412317; Freq_Word2 = 32'd6597070; //4800 bps

Freq_Word1 = 32'd824634; Freq_Word2 = 32'd13194140; //9600 bps

Freq_Word1 = 32'd1649267; Freq_Word2 = 32'd26388279; //19200 bps

Freq_Word1 = 32'd3298535; Freq_Word2 = 32'd52776558; //38400 bps

Freq_Word1 = 32'd3693672; Freq_Word2 = 32'd59098750; //43000 bps

Freq_Word1 = 32'd4810363; Freq_Word2 = 32'd76965814; //56000 bps

Freq_Word1 = 32'd4947802; Freq_Word2 = 32'd79164837; //57600 bps

Freq_Word1 = 32'd9895605; Freq_Word2 = 32'd158329674; //115200bps

Freq_Word1 = 32'd10995116; Freq_Word2 = 32'd175921860; //128000bps

Freq_Word1 = 32'd21990233; Freq_Word2 = 32'd351843721; //256000bps

*****************************************************/

//only want to generate beautiful clk for bsp and sample

reg [31:0] bps_cnt1;

reg [31:0] bps_cnt2;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

bps_cnt1 = 0;

bps_cnt2 = 0;

end

else

begin

bps_cnt1 = bps_cnt1 + 32'd9895605;

//Bps=115200bps

bps_cnt2 = bps_cnt2 + 32'd158329674;

//Bps=115200bps*16

end

end

//------------------------------------------

c++相關文章:c++教程

評論