基于FPGA的VGA可移植模塊終極設(shè)計(jì)

一、VGA的誘惑

本文引用地址:http://www.104case.com/article/190659.htm首先,VGA的驅(qū)動(dòng),這事,一般的單片機(jī)是辦不到的;由于FPGA的速度,以及并行的優(yōu)勢(shì),加上可現(xiàn)場(chǎng)配置的優(yōu)勢(shì),VGA的配置,只有俺們FPGA可以勝任,也只有FPGA可以隨心所欲地配置(當(dāng)然ARM也可以,應(yīng)用比較高吧)。

初學(xué)者就是喜歡看炫的效果,往往會(huì)忍不住想玩。尤其玩FPGA的,沒(méi)玩VGA就感到跟單片機(jī)沒(méi)啥提升,因此VGA的驅(qū)動(dòng)也不得不講。Bingo當(dāng)年也是如此。擋不住VGA的誘惑,初學(xué)者問(wèn)Bingo VGA問(wèn)題的人也是灰常的多,也許一般教科書理論太強(qiáng),實(shí)際應(yīng)用不是很身后,在此Bingo用淺顯易懂的語(yǔ)言來(lái)講述VGA的驅(qū)動(dòng)原理,以及通過(guò)設(shè)計(jì)一個(gè)可移植模塊的應(yīng)用來(lái)講述。

二、VGA驅(qū)動(dòng)原理

此處Bingo不參考任何資料,用當(dāng)年已學(xué)的知識(shí),用淺顯易懂的語(yǔ)言講述。

2、VGA時(shí)序

VGA其實(shí)就是相當(dāng)于一塊芯片,跟單片機(jī)驅(qū)動(dòng)IC一樣,滿足一定的時(shí)序,便能驅(qū)動(dòng)起來(lái)。

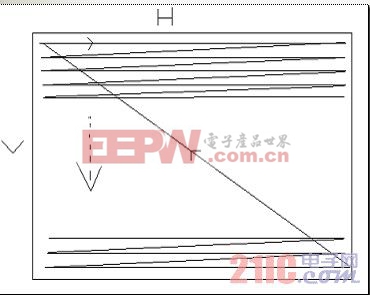

(1)掃描軌跡

VGA的掃描其實(shí)很簡(jiǎn)單,大致軌跡如下所示:

沒(méi)掃描完一行,從新開(kāi)始下一行;每掃完一場(chǎng),重新開(kāi)始下一場(chǎng)。相信你應(yīng)該看的懂。

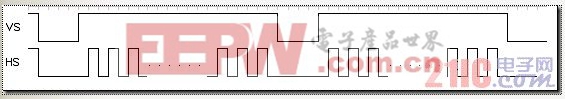

(2)行場(chǎng)掃描

以下是行掃描,場(chǎng)掃描HS,VS時(shí)序圖

如上如所示:VGA一直在掃描,沒(méi)一場(chǎng)的掃描包括了若干行掃描,如此循環(huán)。

(3)VS時(shí)序深入分析

VS時(shí)序如下所示:

可見(jiàn)時(shí)序的循環(huán),可被劃分為a,b,c,d4個(gè)時(shí)期。這四個(gè)時(shí)期定義如下:

A~B:場(chǎng)消隱期 即同步,相當(dāng)于還原掃描坐標(biāo)吧

B~C:場(chǎng)消隱后肩 相當(dāng)于準(zhǔn)備開(kāi)始掃描吧

C~D:場(chǎng)顯示期 掃描中,數(shù)據(jù)有效區(qū)域

D~E:場(chǎng)消隱前肩 完成掃描,相當(dāng)于準(zhǔn)備同步

(4)HS時(shí)序深入分析

可見(jiàn)時(shí)序的循環(huán),可被劃分為a,b,c,d4個(gè)時(shí)期。這四個(gè)時(shí)期定義如下:

A~B:行消隱期 即同步,相當(dāng)于還原掃描坐標(biāo)吧

B~C:行消隱后肩 相當(dāng)于準(zhǔn)備開(kāi)始掃描吧

C~D:行顯示期 掃描中,數(shù)據(jù)有效區(qū)域

D~E:行消隱前肩 完成掃描,相當(dāng)于準(zhǔn)備同步

綜上描述,我們只要知道每個(gè)時(shí)期的時(shí)間,便可以表示出VGA的時(shí)序。而FPGA的工作是由固定頻率的時(shí)鐘觸發(fā)的,因此某固定時(shí)間可以用n次觸發(fā)來(lái)表示。因此我們很容易就想到了FPGA常用的計(jì)數(shù)方法:比如說(shuō)行掃描,我們計(jì)數(shù)0~H_total-1。用另一個(gè)進(jìn)程將其劃分為4個(gè)時(shí)期,安標(biāo)注分配。其實(shí)這相當(dāng)于狀態(tài)機(jī)。

以下是固定分辨率1024*768 60fps下HS,VS的標(biāo)準(zhǔn):

評(píng)論