Altera StratixIV 100G開發方案介紹

Altera公司的Stratix IV 40nm FPGA包括Stratix IV E, Stratix IV GX和Stratix IV GT三個系列, 具有最高的密度(680K 邏輯單元(LE),22.4 Mbits 嵌入式存儲器和1,360個18 x 18 乘法器),最佳的性能以及最低的功耗, 系統帶寬(8.5 Gbps的48 個高速收發器,以及 1,067 Mbps (533 MHz) DDR3存儲器接口)達到了前所未有的水平,并具有優異的信號完整性, 非常適合無線通信,固網,軍事,廣播等其他最終市場中的高端數字應用。本文介紹了Stratix® IV FPGA主要特性, Stratix IV GT器件框圖,以及采用EP4S100G5F45I1 Stratix IV GT FPGA器件的Stratix IV GT 100G開發板主要特性,方框圖,詳細電路圖和材料清單.

本文引用地址:http://www.104case.com/article/190541.htmAltera® Stratix® IV FPGAs deliver a breakthrough level of system bandwidth and power efficiency for high-end applications, allowing you to innovate without compromise. Stratix IV FPGAs are based on the Taiwan Semiconductor Manufacturing Company (TSMC) 40-nm process technology and surpass all other high-end FPGAs, with the highest logic density, most transceivers, and lowest power requirements.

The Stratix IV device family contains three optimized variants to meet different application requirements:

■ Stratix IV E (Enhanced) FPGAs—up to 813,050 logic elements (LEs), 33,294 kilobits

(Kb) RAM, and 1,288 18 x 18 bit multipliers

■ Stratix IV GX transceiver FPGAs—up to 531,200 LEs, 27,376 Kb RAM, 1,288 18 x 18-bit multipliers, and 48 full-duplex clock data recovery (CDR)-based transceivers at up to 8.5 Gbps

■ Stratix IV GT—up to 531,200 LEs, 27,376 Kb RAM, 1,288 18 x 18-bit multipliers, and 48 full-duplex CDR-based transceivers at up to 11.3 Gbps

Stratix® IV FPGA主要特性:

The following list summarizes the Stratix IV device family features:

■ Up to 48 full-duplex CDR-based transceivers in Stratix IV GX and GT devices supporting data rates up to 8.5 Gbps and 11.3 Gbps, respectively

■ Dedicated circuitry to support physical layer functionality for popular serial protocols, such as PCI Express (PCIe) (PIPE) Gen1 and Gen2, Gbps Ethernet (GbE), Serial RapidIO, SONET/SDH, XAUI/HiGig, (OIF) CEI-6G, SD/HD/3G-SDI, Fibre Channel, SFI-5, and Interlaken

■ Complete PCIe protocol solution with embedded PCIe hard IP blocks that implement PHY-MAC layer, Data Link layer, and Transaction layer functionality

■ Programmable transmitter pre-emphasis and receiver equalization circuitry to compensate for frequency-dependent losses in the physical medium

■ Typical physical medium attachment (PMA) power consumption of 100 mW at 3.125 Gbps and 135 mW at 6.375 Gbps per channel

■ 72,600 to 813,050 equivalent LEs per device

■ 7,370 to 33,294 Kb of enhanced TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and FIFO buffers

■ High-speed digital signal processing (DSP) blocks configurable as 9 x 9-bit, 12 x 12-bit, 18 x 18-bit, and 36 x 36-bit full-precision multipliers at up to 600 MHz

■ Up to 16 global clocks (GCLK), 88 regional clocks (RCLK), and 132 periphery clocks (PCLK) per device

■ Programmable power technology that minimizes power while maximizing device performance

■ Up to 1,120 user I/O pins arranged in 24 modular I/O banks that support a wide range of single-ended and differential I/O standards

■ Support for high-speed external memory interfaces including DDR, DDR2, DDR3 SDRAM, RLDRAM II, QDR II, and QDR II+ SRAM on up to 24 modular I/O banks

■ High-speed LVDS I/O support with serializer/deserializer (SERDES), dynamic phase alignment (DPA), and soft-CDR circuitry at data rates up to 1.6 Gbps

■ Support for source-synchronous bus standards, including SGMII, GbE, SPI-4 Phase 2 (POS-PHY Level 4), SFI-4.1, XSBI, UTOPIA IV, NPSI, and CSIX-L1

■ Pinouts for Stratix IV E devices designed to allow migration of designs from Stratix III to Stratix IV E with minimal PCB impact

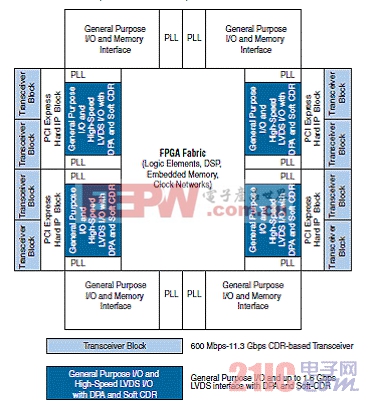

Stratix IV GT Devices

Stratix IV GT devices provide up to 48 CDR-based transceiver channels per device:

■ Thirty-two out of the 48 transceiver channels have dedicated PCS and PMA circuitry and support data rates between 600 Mbps and 11.3 Gbps

■ The remaining 16 transceiver channels have dedicated PMA-only circuitry and support data rates between 600 Mbps and 6.5 Gbps

![]()

圖1. Stratix IV GT器件框圖

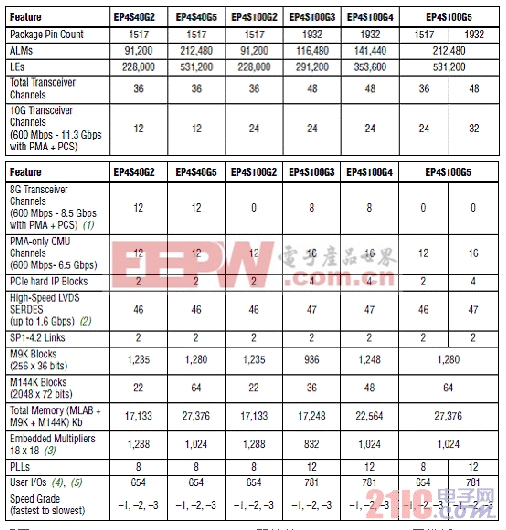

Stratix IV GT器件主要特性:

評論