YUV分離的兩種FPGA實(shí)現(xiàn)

2 基于面積的實(shí)現(xiàn)

面積通常可以通過一個工程運(yùn)行所消耗的觸發(fā)器(FF)和查找表(LUT)數(shù)量已經(jīng)等效門數(shù)量來衡量,即所消耗的資源來衡量。本文基于面積的設(shè)計,充分考慮到用戶對集成度和智能化的要求。對于集成度和智能化的提高,應(yīng)該著眼于每一部分的優(yōu)化,才能獲得整個系統(tǒng)集成度和智能化的提高,因此,本文對YUV分離這個模塊進(jìn)行了研究優(yōu)化。本文引用地址:http://www.104case.com/article/190540.htm

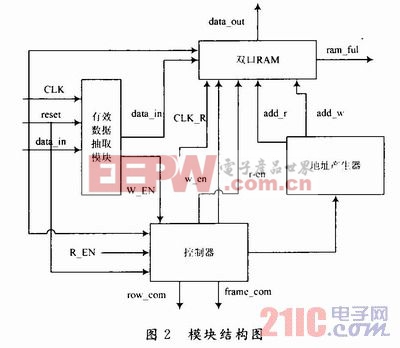

該模塊基于面積的設(shè)計采用一片雙口RAM進(jìn)行模塊結(jié)構(gòu)圖如圖2所示。有效數(shù)據(jù)抽取模塊與控制器和雙口RAM的輸入時鐘應(yīng)與FPGA工作時鐘保持一致。有效數(shù)據(jù)抽取為雙口RAM提供寫使能,每行提供的有效視頻數(shù)據(jù)為704個像素,等到該模塊檢測到有效視頻數(shù)據(jù)的時候,對雙口RAM發(fā)出讀使能,然后接下來利用704個CLK完成對雙口RAM的寫操作,等到寫完畢時向SDRAM發(fā)出滿信號,在SDRAM收到該信號后,產(chǎn)生讀使能,以便對雙口RAM構(gòu)成的讀操作。該模塊的設(shè)計思想是基于FPGA與SDRAM頻率差異進(jìn)行設(shè)計的。一幀視頻數(shù)據(jù)由625行視頻組成,分奇、偶兩場,每一幀都是由有效視頻數(shù)據(jù)和場消隱數(shù)據(jù)組成的。其中23~310和336~623為有效視頻數(shù)據(jù),共576行。其余49行為場消隱數(shù)據(jù),每一行同樣分為行有效數(shù)據(jù)和行消隱數(shù)據(jù)。如果FPGA的工作頻率與SDRAM的頻率滿足一定的差異(本文采用的FPGA頻率為48 MHz,而SDRAM采用100 MHz的時鐘頻率),那么在一行視頻數(shù)據(jù)的有效期完成對雙口RAM的寫入后,在該行視頻數(shù)據(jù)的行消隱期內(nèi),可以通過輸入100 MHz的時鐘來完成對雙口RAM的讀操作。該模塊完成對有效視頻數(shù)據(jù)的寫入需要1 408個CLK,而完成存儲數(shù)據(jù)的讀取需要704個CLK_R,所需時間為1 408×10-8+704×(1/48000000)。因為讀/寫是串行執(zhí)行的,故以后每一行有效視頻的寫入/讀出均需要相同的時間,一行數(shù)據(jù)讀出完畢的仿真如圖3所示。

電子鎮(zhèn)流器相關(guān)文章:電子鎮(zhèn)流器工作原理

評論