多路輸出反激式電源電磁兼容分析

本文引用地址:http://www.104case.com/article/190526.htm

式中:B和S均為矢量。

圖2 差模耦合途徑示意

結合式(1)及式(4)容易推得,寄生磁耦合電感M與涉及的干擾回路面積S成正比例關系。在圖2中,存在有較大的di/dt的回路主要包括變壓器輸入側環路S0,二次側環路S1和S2以及驅動環路S3。

仔細設計電路板走線,盡可能減小上述回路的圍繞面積。將高頻去耦電容Cd0盡量靠近變壓器原邊和MOS管,Cd1盡量靠近負載,以求減小圍繞面積S0與S2,并且要求Cd0和Cd1是低ESR和低ESL的電容器。

電源輸出端至負載的引線應盡可能地短,而且多路輸出每一路都要使用雙絞線,因為,相鄰絞環中在同一導體上產生的電動勢方向相反,相互抵消,這對電磁干擾起到較好的抑制作用。

3.2 減弱共模輻射耦合

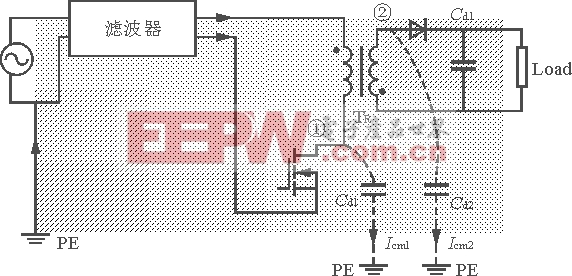

參照圖3,由式(2)可得,共模電流Icm1及Icm2的幅值與兩電氣節點①與②處dv/dt和對PE(安全地)的分布電容Cd1和Cd2的積成正比。圖中節點①是MOS管漏極與變壓器原邊的連接點,節點②為變壓器二次側與輸出二極管的連接點。共模電流輻射強度與共模電流圍繞回路面積有關,也就是說,電磁輻射強度和電流環路面積成正比,這里環路面積用陰影面積表示。因此,減弱共模輻射耦合應從3個方面入手,即減小dv/dt;減小分布電容;減小共模電流環路面積。

圖3 共模耦合途徑示意

節點①及②存在非常大的電壓瞬變,因而在節點①及②處布線應當占用盡可能小的面積,以減小分布電容值。分布電容一般為pF級,因而在低頻段(1MHz)其阻抗影響非常顯著,需要濾波器對共模電流進行衰減,共模扼流圈電感值一般取10~100mH。

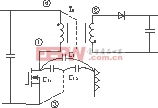

裝在MOS管上的散熱器由于表面積很大,其對節點①的分布電容必須考慮。由圖4可知,采用屏蔽方法將銅箔夾在散熱器和MOS管之間,使原有分布電容Ck變成相互串聯的Ck1和Ck2,從而減小了分布電容。散熱器和變壓器磁芯同樣存在電壓瞬變,將散熱器和磁芯屏蔽分別就近與節點③及④連接,用以抑制散熱器和磁芯的電壓瞬變,并縮短共模電流的耦合路徑。

圖4 減弱共模耦合的措施

3.3 減弱公共阻抗傳導耦合

減弱公共阻抗傳導耦合,就是仔細布線以避免兩電氣回路的公共阻抗部分。其中尤為重要的是地線的鋪設,要遵循“模擬部分地和數字部分地分開,功率部分地和控制部分地分開”的原則。

在實際鋪設中采取了“星狀地”形式,如圖5所示,避免使用環形地。所謂“星狀地”是指不同回路地單獨走線,最后匯集到一點O。O點通常是去耦電容或者濾波電容的陰極。比如在控制芯片周圍,驅動回路的地單獨從控制芯片的去耦電容(O1點)出發,連接到輸入端濾波電容處(O2點),而MOS管源極功率部分引線也直接接入O2點。電壓和電流反饋信號的地線均單獨接入星狀點O1。

圖5 星型鋪地示意

圖5中L1及L2分別為電壓反饋和電流反饋的地線接入端。Cd1為控制(驅動)電路的電源去耦電容,Cd0為輸入濾波電容。

3.4 減弱外部電磁場干擾

設計合理的EMI濾波器。EMI濾波器除能衰減開關電源對電網的EMI之外,還能夠衰減電網引進的部分瞬態干擾。需要強調的是,增加安全地(PE)對衰減共模電流,抑制外界瞬態干擾十分必要。

如圖6所示,在交流進線端并聯高頻CBB電容Ca(2.2nF)和壓敏電阻(VSR)對瞬態電壓進行箝位。

![]()

圖6 利用壓敏電阻抑制瞬態電壓

除了對電路采取局部屏蔽措施外,在調試過程中還使用了整體屏蔽罩,以降低輔助電源子系統對外界的電磁輻射干擾。接入屏蔽罩的輸入、輸出引線(屏蔽線)應當盡量短,并且要妥善接地。[!--empirenews.page--]

3.5 減弱電壓瞬變和電流瞬變

從上述分析可知,EMI的強度都和dv/dt和di/dt成正比。而由變壓器漏感和二極管反向恢復等引起的電壓、電流的過沖和振鈴相比開關周期非常的窄,會造成強的寬頻的瞬態電磁噪聲。因此,在實驗過程中,有針對性地對電路各部分的電壓、電流的過沖和振鈴進行了抑制。

3.5.1 針對開關管

1)考慮減慢MOS管的開關速度,采取增大門極驅動電阻,減小驅動電流來實現。但是要注意適度,因為開關速度越慢,MOS管的開通時間、關斷時間都相應延長,開關損耗隨之增大,會造成開關管過熱,使變流器效率降低。

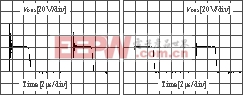

2)采用RCD緩沖電路,吸收變壓器原邊漏感產生的尖峰,減小MOS管的應力,同時減小EMI。當開關管關斷時,變壓器漏感能量轉移到電容C上來,然后由電阻R將這部分能量消耗。圖7(a)及圖7(b)分別為加入吸收電路前后開關管漏源電壓波形,實驗結果表明該電路可進一步吸收漏感Lp(線路寄生電感)和開關管結電容形成的電壓尖峰。

(a) 加吸收電路前 (b) 加吸收電路后

圖7 開關管漏源電壓波形

3.5.2 針對變壓器二次側續流回路

在續流二極管D旁并聯RC吸收電路,同時與續流二極管D串接可飽和磁芯電感Ls,如圖8所示。可飽和磁芯線圈在通過正常電流時磁芯飽和,電感量很小,不會影響電路正常工作;一旦電流要反向流過時,磁芯線圈將產生很大的反電勢,阻止反向電流的上升,因此,將它與二極管D串聯就能有效地抑制二極管的反向浪涌電流。一種小型磁環,可以直接套在二極管的正極引線上,使用很方便。

圖8 接入RC吸收電路和可飽和磁芯

圖9(a)及圖9(b)分別是續流電路采取相應措施前后的續流二極管電壓波形,可見對抑制電壓過沖效果明顯。

(a) 接入RC與Ls前 (b) 接入RC與Ls后

圖9續流二極管電壓波形

3.5.3 針對變壓器的漏感

在反激式拓撲中,可將變壓器等效為理想變壓器和原邊激磁電感的并聯。為了傳送足夠的功率,變壓器必須添加氣隙,以便在磁路中儲存能量,因而磁漏一般都較大。在實際繞制變壓器時,采取了三明治繞法以減小漏感。以其中一組變壓器為例,最里一層為原邊繞組,第二、三層是副邊,最外一層仍是原邊。這種繞法增強了原副邊的耦合程度,減小了變壓器漏感,這樣可以減小開關管上的尖峰電壓,由散熱器回路產生的共模干擾也會大幅度降低。三明治繞法的缺點是原邊繞組從內層到外層穿越了中間的副邊繞組,在變壓器中軸端側絕緣性能大大降低,對于耐高壓實驗是不利的,因而多用在對絕緣性能要求不高的場合。

3.6 反饋環節的調整

在電路調試中,反饋環節調整至關重要,EMI往往是造成反饋環節特性差,電路出現振蕩的主要原因。由于使用的是電流峰值控制,反饋包括電壓和電流反饋。比如,在電流采樣電阻端添加的RC濾波網絡,是一個低通濾波網絡,示波器觀察,添加前后,開關管開通瞬間的電流毛刺降低了約3/4。而電壓反饋開始也采用了RC分壓濾波網絡,即在電阻分壓網絡的接地電阻側并聯濾波電容,容值約為PI調節環電容值的1/10。

調試過程中,曾發生由于接地的不當,使在控制部分和主功率地之間存在分布的共模阻抗,導致電壓輸出端的共模噪聲通過共模阻抗傳導入控制芯片的地,造成占空比丟失,負載調整率不高等問題。當在輸出端接入共模EMI濾波器后,情況大為改觀,振蕩消失。可見在輸出端接入共模濾波器作用明顯。在PCB制版中經過對地線的改進,采用星狀鋪地后,便大大降低了共模噪聲的傳導途徑,即使不接入該濾波器,經過反饋環節自身的PI調整,變換器也同樣趨于穩定。

4 結語

上述的一些方法是針對一個具體的電源,從減小干擾源和切斷干擾途徑來進行分析研究的。由于電路拓撲采取的是硬開關電路,EMI的問題是其比較難以解決的問題。應當說明的是,盡管軟開關工作方式較之硬開關工作方式對減小開關管的電流和電壓應力效果是顯著的,但由于實現軟開關的方式存在多種途徑,其中一些途徑引入的有源及無源元器件在特定工作狀態和本身雜散參數的影響下,亦會成為EMI源,同樣不可忽視。因而是否采用可以降低開關應力的軟開關電路,尚須有關試驗結果來證實。

另外,由于該開關電源存在兩組并聯的情況,各組之間存在未知的干擾,究竟是共模還是差模,需要在實驗中比較檢驗。況且控制電路沒有采用同步方式,不同步的開關相位引起的相互的干擾更加不可預料,有待進一步研究。

評論