基于PN序列幀的同步分析及FPGA實現

PN序列和包含在每個符號中的PN序列求相關后在符號的邊界處會出現第一次峰值,再經過和延時的數據相乘后出現更大的峰值,這個峰值進入移位相關峰的最大值模塊中,連續出現的峰值就能確定符號同步,虛部與實部比值得出的相位角數值可以查對應的表從而得到頻偏估計值,提供頻率補償的參考值。在實際的運用中選取長的PN序列能獲得精確的同步,但是這太浪費帶寬和發射功率,所以在選取一定長度的訓練符時既妻考慮同步的精確度也要考慮系統成本。經過QuartusⅡ8.0工具的設計、編譯、綜合等一系列步驟細同步系統融合成一塊整體模塊,如圖4所示。本文引用地址:http://www.104case.com/article/190516.htm

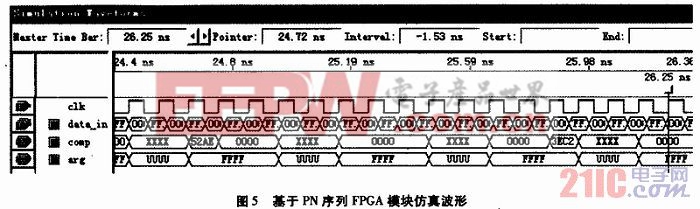

圖5是截取部分的仿真波形,clk輸入時鐘周期是0.10ns,從系統執行運算13.45ns開始到26.25 ns正好是128個時鐘周期,所以此間的comp輸出相關峰幅度的最大值即是數據解調的臨界點,ar8是對應輸出相關峰頻偏的數值。該電路的工作頻率為206.10MHz。

3 結論

上述FPGA實現的是基于數據符號的OFDM系統同步算法,采用Altera公司的芯片EP1S25F102015進行試驗仿真,該芯片有邏輯單元25 660個,存儲模塊單元1 944 576個,DSP模塊單元80個,I/O輸出引腳707個,其中使用的芯片資源使用情況如表1。

基于PN序列幀同步算法實現的FPGA使用了最少的芯片資源,因此時鐘頻率相當快達到了206.10 MHz。盡管這樣,由于有部分序列幀和數據是重疊在一起的,因此在跟蹤到同步的時候解調時,提取在PN序列重疊的那部分數據有一定的難度,它具備時偏和頻偏估計,可以應用于無線通信系統中。綜合算法設計占用芯片資源以及相關情況的分析,算法在FPGA中的實現是可行的和可靠的,充分發揮了FPGA芯片集成密度大、速度快、功耗低、通用性好、適應性強和重復編程的特點。通常可編程邏輯芯片都能提供大容量邏輯單元和存儲單元,因此芯片預留資源都是比較有富余的,考慮信號處理的實性行和可靠性就是我們關注的重點,當然成本也是我們考慮的一個因素,與此同時我們也要考慮電路的設計復雜程度,因為它也要影響數據處理的速度。

評論