基于PN序列幀的同步分析及FPGA實現

由于PN序列和AWGN以及d(n)的相關性很小,所以上式中的最后兩項可以近似為0,從第一項可以看出,當PN序列和包含在每個符號中的PN序列求相關后在符號的邊界處會出現峰值,該峰值可用來實現符號或幀定時。為了實現頻偏估計還必須對相關值移位相乘,即:

式(4)中λ[n,0]表示符號起點的估計值,K表示PN序列的長度,一般而言PN序列的長度和符號的長度一致,但如果在一個符號內疊加k=N/K個相同的PN序列就可以得到更大的頻偏估計范圍,頻偏估計范圍可表示為:

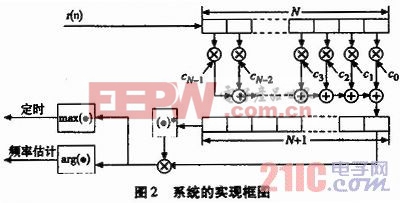

圖2顯示了該算法的系統實現框圖。接收信號與已知的PN序列求相關,PN序列的長度假設為N,然后將求相關后的值存儲在長度為N+1的寄存器內,求其共軛值,并與后N位的值相乘。本文引用地址:http://www.104case.com/article/190516.htm

在多徑信道下,用該算法也能較好地實現幀同步。這是由于用于幀同步的符號中沒有包括數據符號,不會對PN序列產生干擾;PN序列良好的自相關性使得用于幀起點判決的峰值非常尖銳,PN序列越長相關性越好,峰值的能量越大,抗AWGN的能力越強。

2 算法FPGA實現

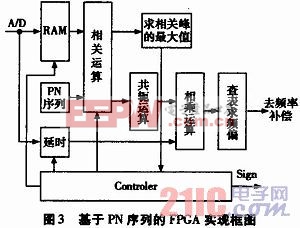

FPGA實現框圖如圖3所示,數據序列通過讀寫寄存器與已知事先存儲的PN序列進行相關運算,讀寫寄存器是雙端的128×16位RAM,PN序列參考IEEE802.11a長訓練符號同步序列(N=52),這里采用128個采樣點,即

PN={1,1,-1,-1,1,1,-1,1,-1,1,1,1,1,1,1,-1,……1,1,1,1}

這128位相關性極強的一系列數據,按地址位編輯成后綴為*mif文件,一旦上電啟動就寫入ROM中,讀地址在讀取RAM的數據時同時也就能依次讀出ROM數據,然后做兩者的相關運算,兩路信號經過相關運算送到下一級求其共軛,共軛結果與后來的輸入延時128位的復數數據再一一相乘,然后進入求移位相關峰的最大值模塊。若連續出現若干個最大峰值,Controler的標志位置高,表明系統可以進行解調處理或者FFT。另外,系統的使能和清零信號也由Controler產生。

評論