HDLC的FPGA實(shí)現(xiàn)方法

7E標(biāo)志加在發(fā)送數(shù)據(jù)段的前后,其時(shí)序由tx_timer確定。在發(fā)送啟動時(shí),先發(fā)7E再發(fā)數(shù)據(jù)。

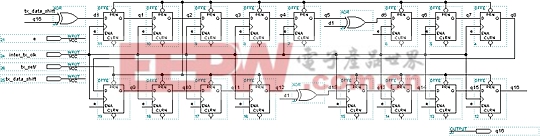

發(fā)送CRC計(jì)算子模塊tx_crc由16個帶賦能端e的D觸發(fā)器組成,其電路圖見圖4,可用來按照x16 + x12 + x5 + 1的生成多項(xiàng)式進(jìn)行16位CRC計(jì)算。該電路的原理可參看數(shù)據(jù)通信教科書,此處不再贅述,僅說明幾點(diǎn):

a. 如果要改變CRC的位數(shù),只要改變D觸發(fā)器的數(shù)量。

b. 如果要改變CRC生成多項(xiàng)式,僅需將多項(xiàng)式中非零系數(shù)項(xiàng)對應(yīng)的D觸發(fā)器的輸出與d1信號異或后送至下一個D觸發(fā)器的輸入。

c. 通過給D觸發(fā)器的PRN端或CLRN端置0,就可改變CRC計(jì)算的初始值。

這個例子可說明用FPGA設(shè)計(jì)的CRC電路具有極大的靈活性。

圖4

發(fā)送的數(shù)據(jù)經(jīng)CRC計(jì)算并將計(jì)算結(jié)果附在數(shù)據(jù)后面,再經(jīng)插零后附上7E標(biāo)志就可輸出。插零操作由子模塊zero_insert完成。子模塊tx_data監(jiān)視著每一個串行移出的數(shù)據(jù),當(dāng)發(fā)現(xiàn)數(shù)據(jù)流中出現(xiàn)五?quot;1時(shí),就輸出控制信號1f_detect/ 暫停數(shù)據(jù)移位,此時(shí)子模塊zero_insert向數(shù)據(jù)流插入一個0比特。

子模塊tx_data中存儲著待發(fā)送數(shù)據(jù)的比特長度值,并隨時(shí)和已發(fā)送數(shù)據(jù)的比特長度值比較。當(dāng)出現(xiàn)兩者相等的情況時(shí),判定為數(shù)據(jù)發(fā)送完畢,子模塊tx_crc停止CRC計(jì)算并把計(jì)算結(jié)果輸出。再經(jīng)過16個數(shù)據(jù)時(shí)鐘后,子模塊7e_generator發(fā)出7E作為結(jié)束標(biāo)志,同時(shí)向接口模塊interface發(fā)出tx_data_empty信號表示數(shù)據(jù)發(fā)送結(jié)束。

3.3 HDLC數(shù)據(jù)接收模塊receiver

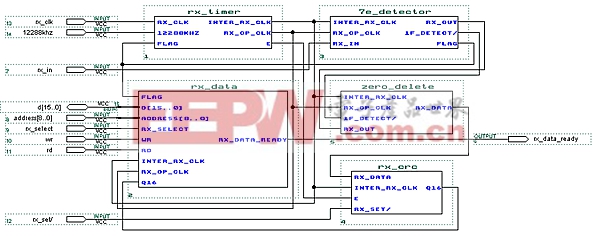

receiver模塊的主要功能是:產(chǎn)生與本路HDLC接收數(shù)據(jù)時(shí)鐘同步的FPGA工作時(shí)鐘;在接收的數(shù)據(jù)流中檢測有無7E標(biāo)志;當(dāng)檢測到數(shù)據(jù)流中有1F信號時(shí),對數(shù)據(jù)進(jìn)行刪零操作;對經(jīng)刪零后的數(shù)據(jù)進(jìn)行CRC校驗(yàn);把接收到的數(shù)據(jù)進(jìn)行串/并轉(zhuǎn)換并存入雙端口RAM;當(dāng)接收到結(jié)束標(biāo)志后,檢查CRC校驗(yàn)值是否正確,向interface模塊發(fā)出rx_data_ready信號。

receiver模塊由接收定時(shí)子模塊rx_timer、接收數(shù)據(jù)子模塊rx_data、標(biāo)志檢測子模塊7e_detector、數(shù)據(jù)刪零子模塊zero_delete、接收CRC校驗(yàn)子模塊 rx_crc等組成,見圖5。

對比receiver模塊和transmitter模塊,雖然兩者一些子模塊的功能是相逆的,但其原理是類似的,因此不再重復(fù)說明。

在receiver模塊中采用了雙端口RAM來作為HDLC接收數(shù)據(jù)緩存器,因此FPGA內(nèi)部向雙端口RAM寫入數(shù)據(jù)和FPGA外部向雙端口RAM讀出數(shù)據(jù)可以分別通過兩個端口獨(dú)立的數(shù)據(jù)地址總線同時(shí)進(jìn)行。

圖5

限于篇幅,以上所述僅為設(shè)計(jì)HDLC電路的大致框架,許多細(xì)節(jié)已被省略了。

4 應(yīng)用實(shí)例

根據(jù)上述設(shè)計(jì)方法,已成功地在可編程邏輯芯片上實(shí)現(xiàn)了多路HDLC的設(shè)計(jì)。

設(shè)計(jì)輸入在Altera公司的MAX+plus II[4] 10.0版本的軟件平臺上進(jìn)行。首先考慮擬設(shè)計(jì)的電路有多少路HDLC收發(fā)器、需要多少內(nèi)部存儲器、工作速率多少、對外部處理器的接口有何要求等。根據(jù)這些考慮,以電路圖和AHDL語言結(jié)合的方法進(jìn)行設(shè)計(jì)輸入。對于時(shí)序電路,主要采用電路圖輸入的方法;對于地址譯碼等功能電路,采用AHDL語言描述;對于存儲器、鎖存器及移位寄存器等,盡量采用MAX+plus II中LPM(參數(shù)化模塊庫)提供的模塊來實(shí)現(xiàn)。全部設(shè)計(jì)輸入完成后,對設(shè)計(jì)進(jìn)行編譯、仿真。在波形仿真器內(nèi)給定輸入信號,檢查輸出的波形是否符合設(shè)計(jì)預(yù)期。反復(fù)多次進(jìn)行修改,確認(rèn)無誤后可將設(shè)計(jì)結(jié)果下載到FPGA芯片。

FPGA芯片選用的是Altera公司的ACEX 1K系列[5]。該系列是Altera公司面向通信和消費(fèi)類數(shù)字產(chǎn)品推出的低功耗、高密度的高性能FPGA集成電路,具有可與ASIC相比擬的價(jià)位。ACEX 1K系列器件內(nèi)部采用基于LUT的架構(gòu),最大邏輯門數(shù)為10萬門;可提供的片內(nèi)存儲器最大為49152比特;最小時(shí)延僅數(shù)納秒,實(shí)際電路總時(shí)延在數(shù)十納秒左右;能夠滿足一般HDLC的要求。ACEX 1K系列FPGA器件工作電壓為2.5伏,I/O接口電壓可選為2.5伏或3.3伏,配置芯片可選Altera公司的EPC1型。

設(shè)計(jì)出的具有多路HDLC功能的FPGA芯片已應(yīng)用于船舶AIS(Automatic Identification System,自動識別系統(tǒng))樣機(jī)的無線數(shù)據(jù)通信鏈路中,成功實(shí)現(xiàn)了雙向數(shù)據(jù)通信。

5 結(jié)束語

FPGA提供了一種取代ASIC芯片的選擇,以上所述僅是用FPGA實(shí)現(xiàn)HDLC功能的一個簡單介紹。在通信產(chǎn)品的設(shè)計(jì)中,如果原已使用了可編程邏輯芯片來實(shí)現(xiàn)某些功能的話,只要改用更大容量的FPGA芯片,就可以將類似于HDLC這樣的功能都集成進(jìn)去。如使用Altera 公司的Quartus II軟件來進(jìn)行同類設(shè)計(jì),則功能更強(qiáng)大,更能支持Top to Down的設(shè)計(jì)方法,并且支持Cyclone等大規(guī)模FPGA芯片。此外,Xilinx公司新推出90納米工藝的Spartan-3系列低成本FPGA芯片,也可作為取代ASIC的一種選擇。顯然,F(xiàn)PGA在通信技術(shù)中的應(yīng)用十分值得重視,并正受到越來越多的關(guān)注。(2003.11)

參考文獻(xiàn)

1 張德民. 數(shù)據(jù)通信,P.194. 北京:科學(xué)技術(shù)文獻(xiàn)出版社,1997.8

2 ISO/IEC 3309: Information technology-Telecommunications and information exchange between systems-High-level data link control (HDLC) procedures-Frame structure, P.4. Switzerland: International Electrotechnical Commission, Jun 2002

3 Zarlink Semiconductor. MT8952B HDLC Protocol Controller, P.3-64. March 1997

4 Altera Corporation. MAX+plus II, Version 10.0, Sep 2000

5 Altera Corporation. ACEX 1K Programmable Logic Family Data Sheet, Altera Digital Library,Version 3,2001

評論