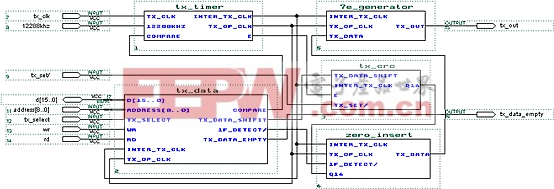

圖3

待發送數據是由外部CPU通過interface模塊寫入指定地址的緩沖存儲器的。在HDLC中,可以選用的緩沖存儲器類型有FIFO(先進先出)存儲器、DPRAM(雙端口RAM)存儲器、移位寄存器等。在本設計中,發送數據的存儲使用的是數據鎖存移位寄存器。使用這種寄存器的優點是:寫入的待發送數據經鎖存后,可在任何時候(包括正在發送時)對數據的任何部分讀出檢查,并且數據可直接串行移位做CRC計算,簡化FPGA設計。這種寄存器由數據鎖存器和串行移位寄存器兩部分組成,占用芯片資源較多,但對于有大量片上存儲器可用的FPGA 芯片來說,這點是不成問題的。

評論