CCD系統下基于FPGA的PCI圖像采集卡設計與實現

3.2 PCI接口的設計

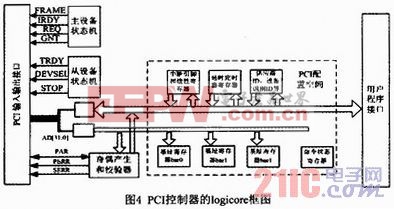

PCI圖像采集卡的接口設計非常重要。由于PCI總線規范復雜,設計復雜,為了加快開發周期,采用Xilinx提供的PCI core來完成PCI總線控制器的設計。PCI控制器核logic core的內部框圖如圖4所示。本文引用地址:http://www.104case.com/article/190453.htm

PCI控制核主要完成用戶設備和PCI總線之間的數據傳輸。PCI核可工作在Target傳輸模式和Initiator傳輸模式。每種傳輸模式又可以分單次傳輸和突發傳輸。由于單次傳輸速度達不到要求,我們選擇突發傳輸模式以便提高傳輸速度。

Target模式下的突發傳輸模式相對Initiator下的突發傳輸模式的控制邏輯簡單,但是考慮到PCI圖像采集卡的可移植性,故采用Initia tor突發傳輸模式。在Initiator突發傳輸模式下,PCI圖像采集卡主動向橋芯片申請PCI總線控制權,并主動傳送數據;在Target模式下,必須用軟件對橋芯片進行配置,也就是說PCI圖像采集卡作為一個PCI從設備等待橋芯片的配置、數據讀取等。所以采用Initiator下的突發傳輸模式邏輯控制復雜,但是移植性好。

3.3 PCI圖像采集卡地址空間配置

PCI的地址空間可分為三種,分別是PCI配置空間、PCI I/O空間和PCI內存空間。

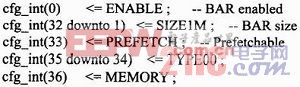

我們需要對PCI核進行配置。

Xilinx提供的PCI核提供了BAR0、BAR1、BAR2三個地址空間。這三個地址空間可以配置成內存地址空間或I/O地址空間。為了PCI圖像采集卡在不同橋芯片下和不同的操作系統下工作。我們把所有的地址空間都配置成了內存空間,因為不是所有處理器都支持I/O操作。在我們的設計中,使用了BAR0和BAR1兩個地址空間,配置成了內存空間,并全部配置成可以預取模式。以配制BAR0為例說明配置方法。

3.4 地址指針的設計

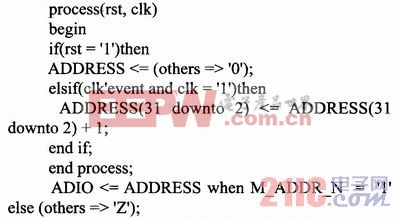

對于Initiator下的突發模式傳輸,因為從設備可以在任何時刻結束數據的傳輸,應用程序必須始終對地址進行跟蹤,以便在Initiator再次發起傳輸時能得到正確的地址進行重新傳送。

我們在設計的時候用了一個32bit的寄存器對地址進行跟蹤,其中低2位始終為0,高30位用來保存數據。利用M_DATA_VLD信號來控制地址的增加。當M_ADDR_N有效的時候把地址輸送到地址總線上。

3.5 Initiator突發數據傳輸狀態機的實現

狀態機用來控制突發模式的讀寫時序。整個狀態機由六個狀態組成,分別是IDLES、REOS、WRITES、READS、RSTS、OOPS。下面分對這六

個狀態的功能進行描述。

IDLES:狀態機處于空閑狀態,狀態機等待用戶發起讀或者寫請求。

REOS:用戶發起了傳送請求。當是讀請求時,狀態機進入READS狀態。當是寫請求時,狀態機進入WRITES狀態。

READS:狀態機一直處于數據讀取狀態直到傳輸完成,或者在傳輸過程中發生了不可恢復的錯誤。當數據正常傳輸完成時,狀態機會跳到OOPS_S狀態;當發生致命錯誤時,狀態機會處于RSTS。

WRITES:狀態WRITES和READS基本類似。不同的是數據傳輸方向不同。

RSTS:當狀態機處于RSTS時說明整個系統發生了不可恢復的錯誤,必須重新復位讓軟硬件。

OOPS:當狀態機處于OOPS狀態,如果需要對前端的FIFO進行回滾操作,狀態機就一直處于OOPS。如果前端FIFO檢測傳輸完成信號,完成則進入IDLES狀態,否則進入申請總線狀態REQS。

3.6 異步存儲器的實現

由于PCI讀存儲器的時鐘頻率和數據寬度與收發器寫存儲器的時鐘頻率和數據寬度不一致,所以要設計在兩個異步時鐘之間傳輸數據的接口電路。Xilinx自帶的FIFO IP核是一種解決方案。但是由于異步FIFO沒有Initiator突發數據傳輸下的需要的back_up信號,所以利用Xilinx自帶的塊RAM作為數據寬度可以控制的存儲器。

評論