基于DSP+FPGA的高精度程控交流電源設計

3.2 逆變電路設計

逆變電路采用SPWM方式。由于調制后的信號中除含有調制信號和高頻率的載波頻率及載波倍頻附近的頻率分量外,幾乎不含其他諧波。因此,提高開關頻率可消除逆變器的低次諧波,減小諧波損耗,但開關頻率過高會使逆變器的開關損耗及電磁干擾大幅增加,同時給DSP的運算及D/A轉換帶來壓力。此外,死區時間在脈寬中所占的比例過大也會造成占空比丟失。因此,從開關器件的損耗、諧波失真度之間折中,選取開關頻率為80 kHz。由于單極性調制產生的波形失真較大,這里采用雙極性調制技術。全橋的4個功率管都工作在較高的載波頻率,同一橋臂的兩個功率管互補導通,可得到較為理想的輸出波形。

為降低調制復雜程度,采用異步方式SPWM技術實現頻率輸出的精密控制,保持調制頻率(即開關頻率)fc固定不變,通過改變載波比N完成fo的變化。由于電源最高輸出頻率只有1 kHz,所以N較大,一周期內脈沖數較多,脈沖不對稱產生的不利影響較小。

設計中采用電壓跟蹤控制方法生成SPWM波形,可實現高精度輸出。該方法具有高頻濾波設計簡單,輸出諧波小的優點,其產生的誤差在工程上可忽略不計。工作原理如下:采用閉環控制,將希望輸出的波形作為指令信號U*,將實際波形作為反饋信號U,通過兩者的瞬時值比較來決定逆變電路各器件的通斷,使實際的輸出跟蹤指令信號變化。在比較控制過程中,設置一個固定的時鐘,以固定采樣周期對指令信號和被控量采樣,按偏差的極性來控制開關器件通斷。在時鐘信號到來時刻,若UU*,令功率開關導通,使U增大;若U>U*,則令功率開關關斷,使U減小。這樣,各采樣時刻的控制作用都使實際電壓與指令電壓的誤差減小,只要N足夠大,即可保證電壓跟蹤控制精度。考慮到功率器件的開通和關斷都需要時間,為防止上下臂直通造成短路,需設置一定的死區時間。因此,實際電路工作時,考慮到功率器件的開通和關斷時間,調制度M=0.85。最大輸出電壓有效值為300 V,故前級電壓輸出應為:![]() /0.85=500V。逆變電路關鍵參數設計過程如下:

/0.85=500V。逆變電路關鍵參數設計過程如下:

(1)輸出濾波器的設計

①濾波電感:最大紋波電流取滿功率輸出正弦電流峰值的30%,即![]() 。而紋波電流△i=[(ui-Uo)/L](D/fs)=(ui-uo)uo/(Lui),其中ui為前級輸出電壓,D為占空比。由上式可知,當uo=0.5ui時,△i最大,故有:△Imax=ui/(4Lfs),所以L=1.49 mH,取1.5 mH。

。而紋波電流△i=[(ui-Uo)/L](D/fs)=(ui-uo)uo/(Lui),其中ui為前級輸出電壓,D為占空比。由上式可知,當uo=0.5ui時,△i最大,故有:△Imax=ui/(4Lfs),所以L=1.49 mH,取1.5 mH。

②濾波電容:濾波電感、電容一起構成低通濾波器。SPWM方式下,為濾除高次諧波成分,取濾波器截至頻率為開關頻率的1/10,即![]() (2πfs)/10,故C=0.26μF。為消除器件非理想特性及死區等影響,電容值需大一些,設計中取為1μF。

(2πfs)/10,故C=0.26μF。為消除器件非理想特性及死區等影響,電容值需大一些,設計中取為1μF。

(2)陷波器的設計

為進一步降低諧波失真,在輸出濾波器后側設置了兩級陷波器電路,電路如圖3所示。

圖中,L1與C1構成第一級陷波器,用于濾除開關頻率噪聲,諧振頻率取fs(80 kHz),取C1=2μF,則L1=[1/(2πfs)2]/C1=2μH;L2與C2構成第二級陷波器,濾除開關頻率二倍頻噪聲。諧振頻率取為160 kHz,取C2=2μF,則L2=500 nH。

4 實驗結果

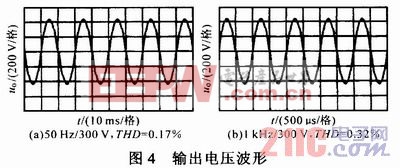

在樣機上進行了實驗驗證。額定輸出功率750 VA,可實現頻率變化范圍45 Hz~1 kHz,頻率分辨率為10 μHz,電壓變化范圍0~300 V。滿載300 V正弦電壓輸出波形uo如圖4所示。

評論