基于改進的布斯算法FPGA嵌入式18×18乘法器

典型的4-2壓縮是由2個3-2壓縮構成的,其延遲為4個異或。圖3為一個優化了的4-2壓縮,其延遲為3個異或的延遲。因此9-2壓縮樹從頂層到最終輸出僅過了7個異或門的延遲。

4 35 b兩級超前進位加法器

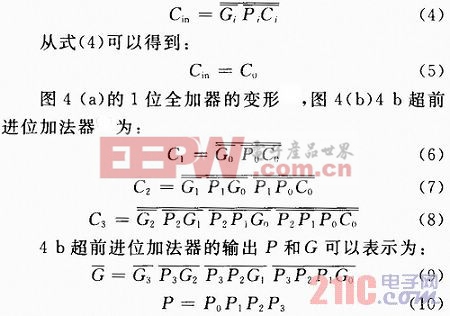

超前進位加法器對乘法器的整體性能的影響至關重要,要想提高乘法器的速度,超前進位加法器也必須進行必要的優化。在此采取基于4 b超前進位加法器的兩級加法器。

由于進位鏈延遲時間隨著輸入的增加而增加,必須考慮到輸入信號的個數,在面積和速度中進行折中發現4 b超前進位加法器是最適合作為基本的模塊。

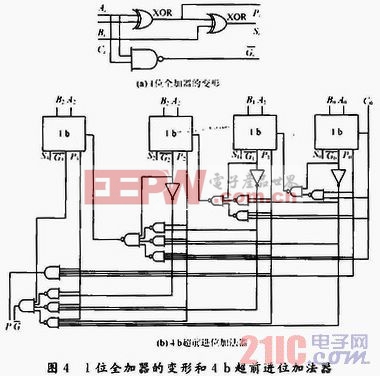

從圖4(b)中可以看到在4 b超前進位加法器中,除了P和G由與門實現的,其他的都是有與非門實現的。

圖4(a)為1位全加器的變形,有3個輸入Ai,Bi,Ci和三個輸出Pi,Si和Gi,其中Ai和Bi為兩個加數,Cin為進位輸入,Pi和Gi分別為進位傳輸和進位產生,而Si為第i位的和。

采用基于4 b的超前進位加法器來組成16 b超前進位加法器,進位鏈采取與4 b超前進位鏈相同的結構。同樣的分析方法,發現16 b的P和G延時為5個門的延遲。用2個16 b的超前進位加法器和一個3 b超前進位加法器組成35 b超前進位加法器,其進位鏈采取與上面相同的方法。研究不難發現,經過7個門延遲進位到達3 b超前進位加法器,再經過3個門的延遲得到第35位的結果。也就是說整個加法器僅僅經過10個門的延遲。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論