一種基于FPGA的UART 電路實現

1 引 言

本文引用地址:http://www.104case.com/article/190344.htmUART 即通用異步收發器,他廣泛使用串行數據傳輸協議。UART 功能包括微處理器接口、用于數據傳輸的緩沖器(Buffer)、幀產生、奇偶校驗、并串轉換,用于數據接收的緩沖器、幀產生、奇偶校驗、串并轉換等。UART的特點是一個字符接一個字符傳輸,并且傳送一個字符總是以起始位開始,以停止位結束,字符之間沒有固定的時間間隔要求。每一個字符的前面都有一位起始位(低電平,邏輯值0) , 字符本身由5~ 8 位數據位組成,接著字符后面是一位校驗位,最后是停止位(1 位,或1 位半,或2位) , 停止位后面是不定長度的空閑位。停止位和空閑位都規定高電平(邏輯值1) , 這樣可以保證起始位開始處有一個下降沿。在一般的使用中往往不需要使用完整的UART功能,比如對于多串口的設備或需要加密通訊的場合使用UART 就不是最合適的。如果設計上用到FPGA ?CPLD器件,那么就可以將所需要的UART 功能集成到FPGA內部,從而使整個設計更加緊湊、穩定、可靠。分析UART的結構,UART 主要由數據總線接口、控制邏輯和狀態接口、波特率發生器、發送和接收等部分組成。在本設計中,固定數據幀格式為: 開始位(1 b 低電平)、8 位數據位、偶校驗、停止位(1 b 高電平) , 波特率可調。

2 波特率發生模塊

設計的UART 的接收和發送按照相同的波特率進行,波特率可以通過接口模塊的總線接口進行設置。

UART 收發的每一個數據寬度都是波特率發生器輸出的時鐘周期的16 倍,即假定當前按照9 600 b?s 進行收發,那么波特率發生器的輸出時鐘頻率應該為9 600×16 Hz.

假定提供的外部時鐘為116MHz, 可以很簡單地通過總線寫入不同的數值到波特率發生器保持寄存器,然后用計數器的方式生成所需要的各種波特率,即分頻器。計算公式為: 1 600 000?(16×所期望的波特率) - 1, 如果希望輸出10 000 Hz 的波特率,可以得出從總線寫入的數值為1 600 000?(16×10 000) - 1= 9 (09H)。

3 發送模塊

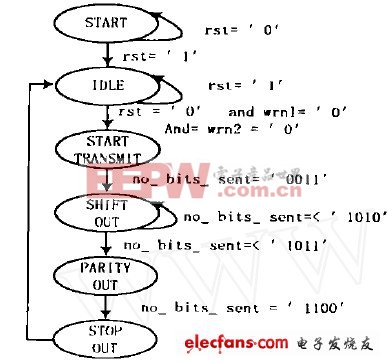

根據UART 協議的描述,發送邏輯流程如圖1 所示。

發送數據由接口模塊控制,接口模塊給出w rn 信號,發送器根據此信號將并行數據鎖存,并通過發送保持寄存器和發送移位寄存器發送并行數據。由計數器no_ bs_sent 控制狀態的轉移,即數據的發送,計數值為1 時,數據從發送保持寄存器傳送到發送移位寄存器,計數值為2時,發送開始位(1 b 低電平) , 計數值為3~ 10, 發送8 位數據,計數器為11, 發送校驗位,計數值為12, 發送1 位停止位,計數器隨后清零。發送時鐘是根據數據傳輸的波特率產生的,16 倍于波特率發生器產生的時鐘。

圖1 發送邏輯的流程

發送模塊信號:

rst (輸入) : 復位端口, 低電平有效;

w rn (輸入) : 寫控制信號;

din [ 0: 7 ] (輸入) : 并行數據輸入信號;

clk16x (輸入) : 外部時鐘信號;

tbre (輸出) : 發送保持寄存器空信號, 高電平有效;

t sre (輸出) : 發送移位寄存器空信號, 高電平有效;

sdo (輸出) : 串行數據輸出信號。

用VHDL 語言編寫代碼,使用Xinlinx 的ISE511 進行邏輯綜合,運用Modelsim 7.2 做時序仿真,其結果如圖2所示。

圖2 發送模塊時序仿真波形圖

4 接收模塊

根據UART 的協議描述,可以畫出如圖3 所示的接收邏輯流程圖。接收邏輯首先通過檢測輸入數據的下降沿來檢查起始位,然后產生接收時鐘,利用接收時鐘來采樣串行輸入數據,在緩沖器中作移位操作,同時產生校驗位,在第9 位處比較校驗位是否正確,在第10 位處比較停止位是否為高,在校驗位錯誤或停止位錯誤的情況下產生錯誤指示信號。接收時鐘是根據數據傳輸的波特率產生的,16 倍于波特率發生器產生的時鐘。

接收模塊信號:

rst (輸入) : 復位信號;

clk16x (輸入) : 輸入時鐘;

rdn (輸入) : 讀鎖存信號;

rxd (輸入) : 串行數據輸入信號;

dout [ 0: 7 ] (輸出) : 并行數據輸出總線;

fram ing_ erro r (輸出) : 幀錯誤信號;

parity_ erro r (輸出) : 校驗錯誤信號;

data_ ready (輸出) : 數據接收完畢信號。

評論