用ARM對FPGA進行配置的原理與方法

0引言

本文引用地址:http://www.104case.com/article/190330.htm基于SRAM工藝FPGA在每次上電后需要進行配置,通常情況下FPGA的配置文件由片外專用的EPROM來加載。這種傳統配置方式是在FPGA的功能相對穩定的情況下采用的。在系統設計要求配置速度高、容量大、以及遠程升級時,這種方法就顯得很不實際也不方便。本文介紹了通過ARM對可編程器件進行配置的的設計和實現。

1 配置原理與方式

1.1配置原理

在FPGA正常工作時,配置數據存儲在SRAM單元中,這個SRAM單元也被稱為配置存儲器(Configuration RAM)。由于SRAM是易失性的存儲器,因此FPGA在上電之后,外部電路需要將配置數據重新載入到片內的配置RAM中。在芯片配置完成后,內部的寄存器以及I/O管腳必須進行初始化。等初始化完成以后,芯片才會按照用戶設計的功能正常工作。

1.2配置方式

根據FPGA在配置電路中的角色,其配置數據可以使用3種方式載入到目標器件中:

·FPGA主動(Active)方式;

·FPGA 被動(Passive)方式;

·JTAG 方式;

在FPGA 主動方式下,由目標FPGA來主動輸出控制和同步信號(包括配置時鐘)給專用的一種串行配置芯片,在配置芯片收到命令后,就把配置數據發到FPGA,完成配置過程。在被動方式下,由系統中的其他設備發起并控制配置過程,FPGA只輸出一些狀態信號來配合配置過程。被動方式包括被動串行PS(Passive Serial )、快速被動并行FPP(Fast Passive Parallel)、被動并行同步PPS(Passive Parallel Serial)、被動并行異步PPA(Passive Parallel Asynchronous)、以及被動串行異步PSA(Passive Serial Asynchronous)。JTAG是IEEE 1149.1邊界掃描測試的標準接口。從JTAG接口進行配置可以使用Altera的下載電纜,通過Quartus工具下載,也可以采用微處理器來模擬 JTAG時序進行配置。

2硬件電路設計

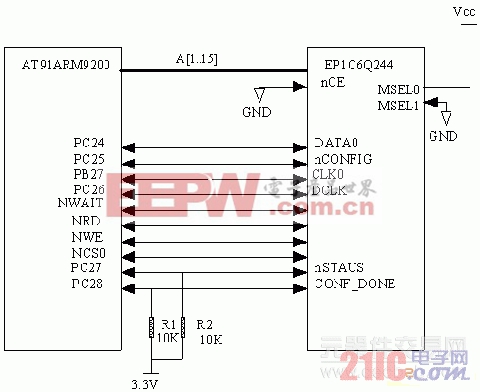

AT91ARM9200對EP1C6配置的硬件電路示意圖如圖1所示。

在配置FPGA時,首先需要將年nCONFIG拉低(至少40us), 然后拉高。當nCONFIG被拉高后,FPGA的nSTATUS也將變高,表示這時已經可以開始配置,外部電路就可以用DCLK的時鐘上升沿一位一位地將配置數據寫進FPGA中。當最后一個比特數據寫入以后,CONFIG_DONE管腳被FPGA釋放,被外部的上拉電阻拉高,FPGA隨即進入初始化狀態。

3軟件設計

本文在設計時使用Linux系統,軟件編寫和調試是在ADS 下。主要程序如下:

評論